| Home | Theory | Evaluation | Code | Applications | Hardware | Publications | News | People | Workshops |

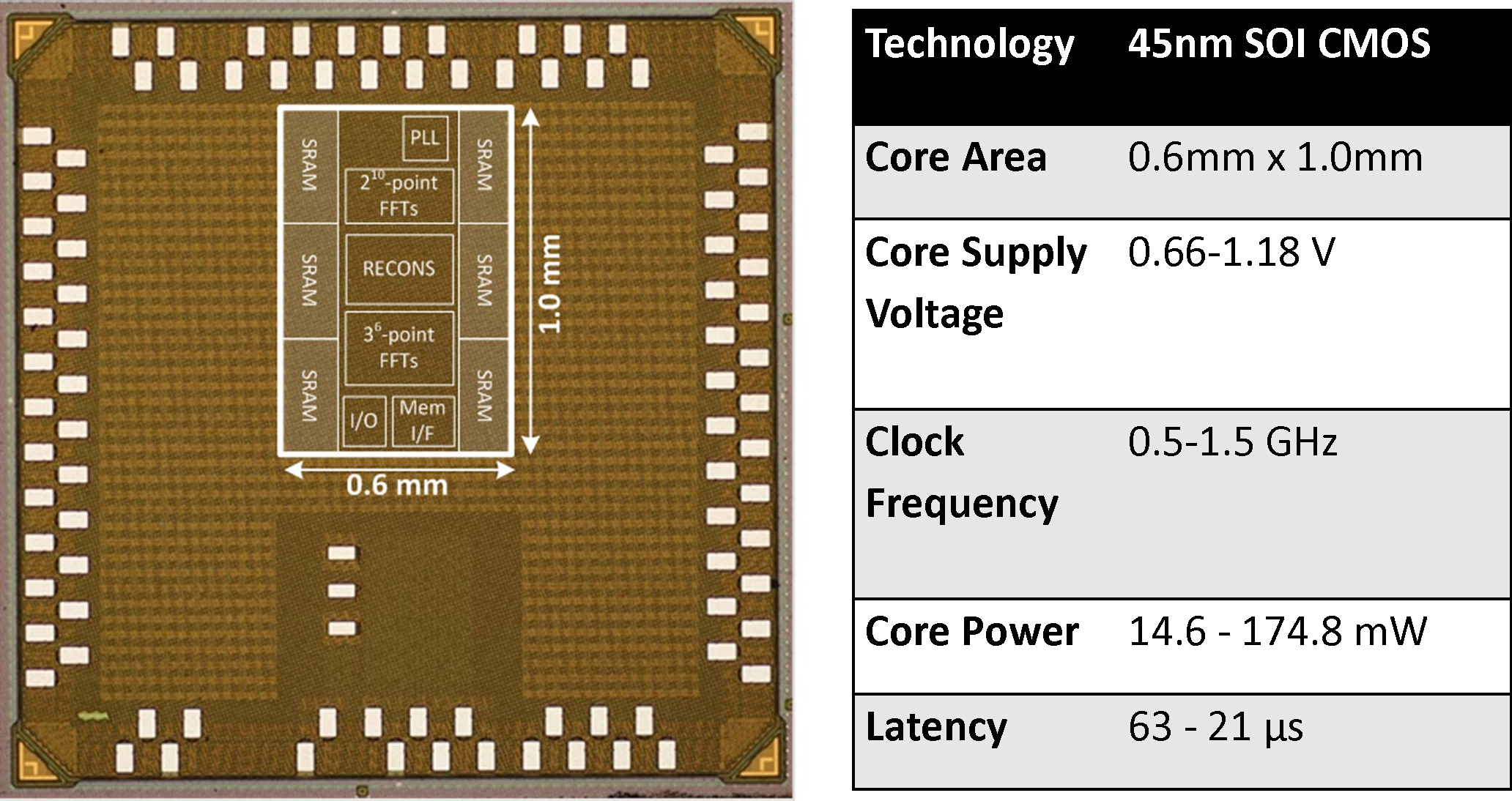

SFFT IC Chip: A VLSI implementation of SFFT: The chip implements a 746,496-point SFFT, in 0.6mm^2 of silicon area. At 0.66V, it consumes 0.4pJ/sample and has an effective throughput of 36GS/s. The chip implements an SFFT algorithm based on the paper [Allerton'13]. Additional details of the ASIC implementation can be found in: A 0.75 Million-Point Fourier Transform Chip for Frequency-Sparse Signals O. Abari, E. Hamed, H. Hassanieh, A. Agarwal, D. Katabi, A. Chandrakasan, and V. Stojanovic. ISSCC, February 2014. [PAPER] [SLIDES] SFFT FPGA Implementation:A high-throughput FPGA implementation of SFFT: The implementation performs a million-point sparse Fourier Transform every 1.16 milliseconds andcan process streamed input data at 0.86GS/s. The FPGA implementation is based on the SFFT algorithm from the paper [SODA'12].Additional details of the FPGA implementation can be found in: High-Throughput Implementation of a Million-Point Sparse Fourier Transform Abhinav Agarwal, Haitham Hassanieh, Omid Abari, Ezz Hamed, Dina Katabi, and Arvind FPL, September 2014. [PAPER] |