# **Dynamic Zero Compression** for Cache Energy Reduction

Luis Villa Michael Zhang Krste Asanovic

{luisv|rzhang|krste}@lcs.mit.edu

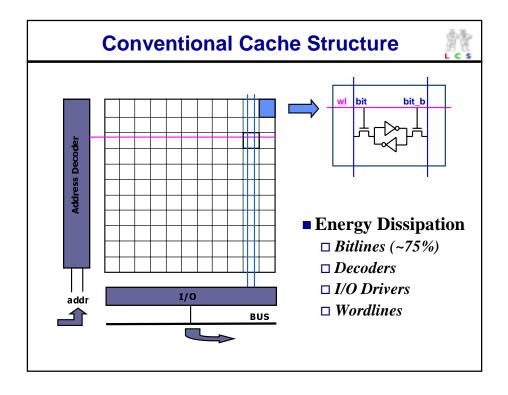

#### **Existing Energy Reduction Techniques** 128 32 ばー Sub-banking gwl Hierarchical Bitlines lwi **■** Low-swing Bitlines SRAM □Only for reads, writes SRAM Cells Cells performed full swing. **■** Wordline Gating Offset addr offset offset I/O BUS

## **Asymmetry of Bits in Cache**

- >70% of the bits in D-cache accesses are "0"s

- □ Measured from SPECint95 and MediaBench

- □ Examples: *small values*, *data types*

- **■** Related work with single-ended bitlines

- □ [Tseng and Asanovic '00] --- Used in register file design with single-ended bitlines.

- □ [Chang et. al. '99] --- Used in ROM and small RAM with single-ended bitlines.

- Differential bitlines preferred in large *SRAM* designs.

- **□** Better Noise Immunity

- **□** Faster Sensing

## **Hardware Modifications**

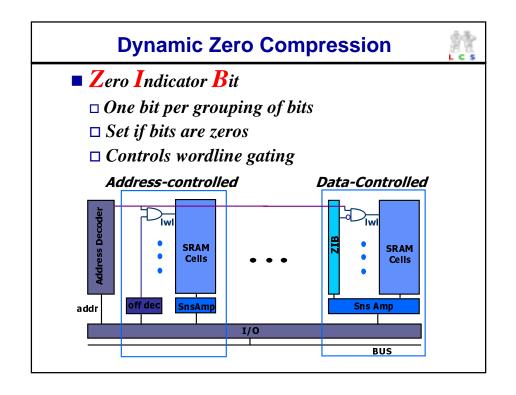

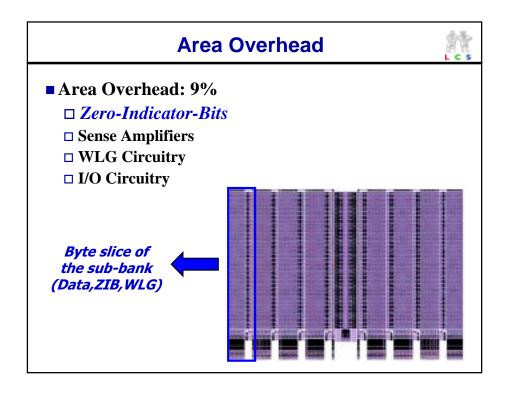

- Zero Indicator Bit

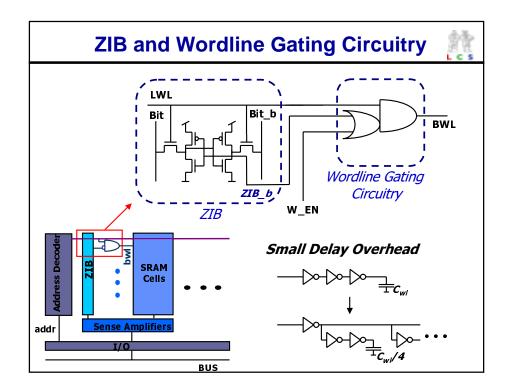

- **■** Wordline Gating Circuitry

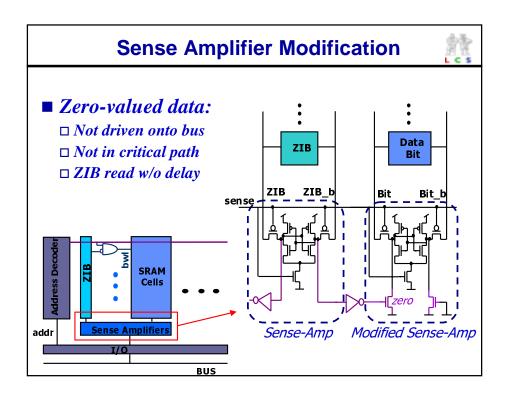

- **Sense Amplifier**

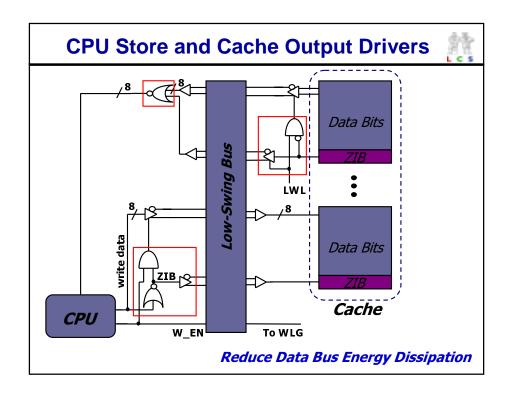

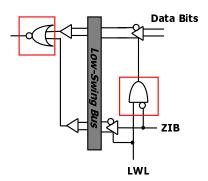

- **CPU Store Driver**

- Cache Output Driver

## **Delay Overhead**

- No delay overhead for writes

- $\hfill\Box$  Zero check performed in parallel with tag check

- 2 F04 gate-delays for reads

- $\hfill\Box$  A pessimistic 7% worst case delay

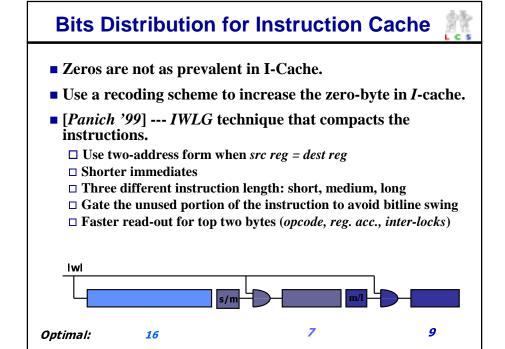

## **IWLG to Dynamic Zero Compression**

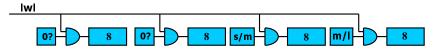

- Adopting IWLG technique for Dynamic Zero Compression

- □ Small modification on instruction format

- Use 8-8-8 instead of 16-7-9

- □ Upper two byte are zero-detected

- ☐ Lower two bytes are usage-detected

- □ Able to eliminate bitline swings of zero-valued bytes in 2 upper bytes

- Example: Opcode 000000

- □ Slower than IWLG due to wordline gating in the critical path

#### **Conclusion**

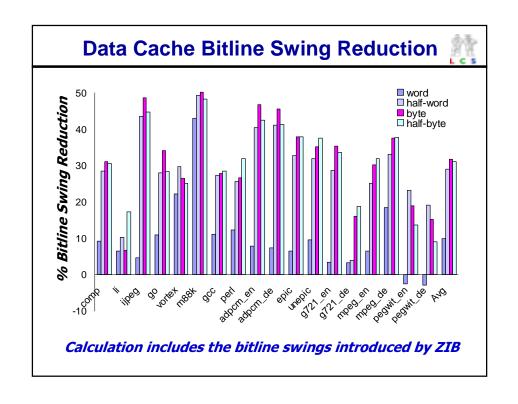

- A novel hardware technique to reduce cache energy by eliminating the access of zero bytes.

- □ Small area and delay overhead

- Area: 9%, Delay: 2 F04 gate-delays

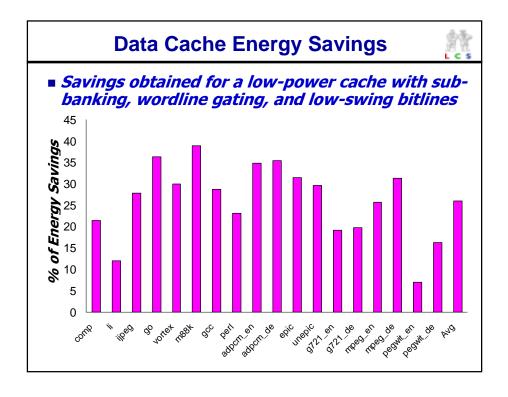

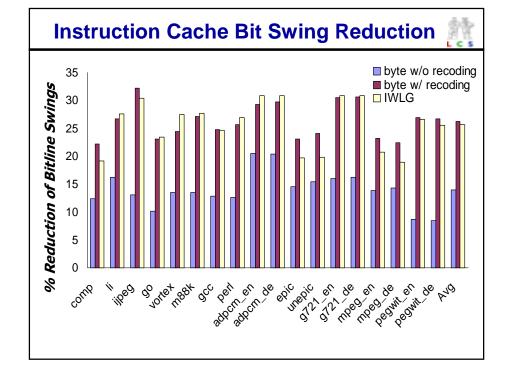

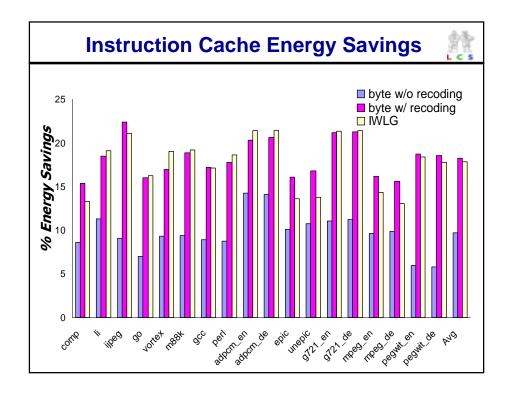

- □ Average energy saving: D-Cache: 26%, I-Cache: 18%

- Processor wide: ~10% for typical embedded processors

- □ Completely orthogonal to existing energy reduction techniques

- Dynamic Zero Compression is applicable to

- □ Second level caches

- $\square$  **DRAM**

- □ Datapath [Canal et. al. Micro-33]

## Thank You!

http://www.cag.lcs.mit.edu/scale/