# **ATB0 Engineering Document - Controller**

SCALE Group MIT Computer Science and Artificial Intelligence Laboratory

# Contents

| 1 | Intro | oduction                                      | 5  |

|---|-------|-----------------------------------------------|----|

| 2 | User  | r Interface                                   | 6  |

|   | 2.1   | Accessing SDRAM                               | 6  |

|   | 2.2   | Configuration                                 | 8  |

|   |       | 2.2.1 Setting the voltage                     | 8  |

|   |       | 2.2.2 Measuring the current                   | 10 |

|   |       | 2.2.3 Calibrating current measurement         | 10 |

|   |       | 2.2.4 Setting the generated clock speed       | 11 |

|   |       | 2.2.5 Other configuration registers           | 11 |

|   | 2.3   | Communication with the daughtercard           | 12 |

|   |       | 2.3.1 Accessing the user pins                 | 12 |

|   |       | 2.3.2 Asynchronous Host Interface Port (AHIP) | 13 |

|   |       | 2.3.2.1 Asynchronous Transaction Protocol     | 13 |

|   |       | 2.3.2.2 Writing and reading with AHIP         | 14 |

|   |       | 2.3.2.3 8 bit reads and writes                | 14 |

|   |       | 2.3.2.4 AHIP Self-Test                        | 15 |

| • |       |                                               |    |

| 3 | -     | lementation details                           | 16 |

|   | 3.1   | 6                                             | 16 |

|   | 2.2   |                                               | 17 |

|   | 3.2   | 1                                             | 17 |

|   |       | 3.2.1 Shift registers                         | 17 |

|   | 2.2   | 3.2.2 Counter                                 | 18 |

|   | 3.3   | Controller module                             | 18 |

|   | 3.4   | Decode module                                 | 19 |

|   |       | 3.4.1 PLX Interface                           | 19 |

|   | 2.5   | 3.4.2 Decode implementation                   | 20 |

|   | 3.5   | SDRAM control module                          | 24 |

|   |       | 3.5.1 Refresh Timer                           | 25 |

|   | 2.6   | 3.5.2 SDRAM control module implementation.    | 25 |

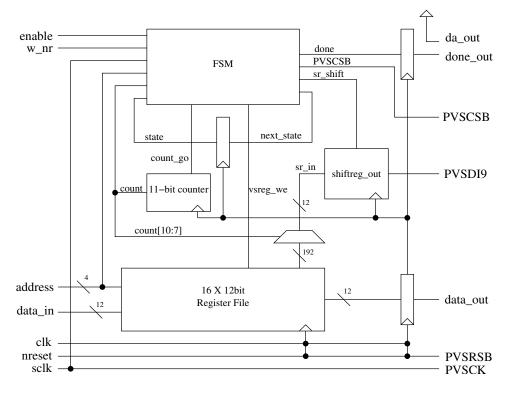

|   | 3.6   | Voltage Set module                            | 30 |

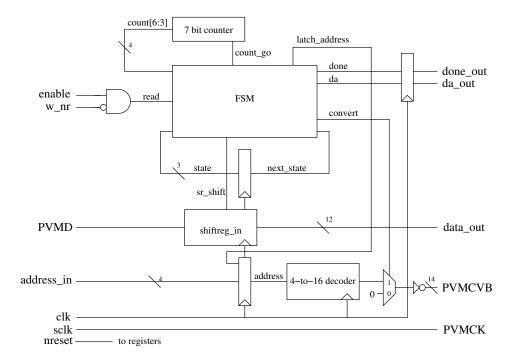

|   | 3.7   | Voltage measure module                        |    |

|   | 3.8   | Current measure module                        |    |

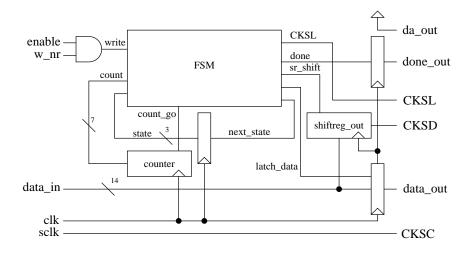

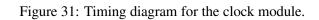

|   | 3.9   | Clock module                                  | 39 |

|   |       | User pin control module                       | 41 |

|   |       | AHIP module                                   | 42 |

|   | 3.12  | LGALED module                                 | 46 |

| A | Pino  | out listings                                  | 48 |

# List of Figures

| 1  | Block diagram of ATB0                                                |

|----|----------------------------------------------------------------------|

| 2  | ATB0 Memory Map                                                      |

| 3  | SDRAM memory layout                                                  |

| 4  | Format of VMR <i>mn</i>                                              |

| 5  | Calibrating the current                                              |

| 6  | Clock register format                                                |

| 7  | Status register format                                               |

| 8  | AHIP Header format                                                   |

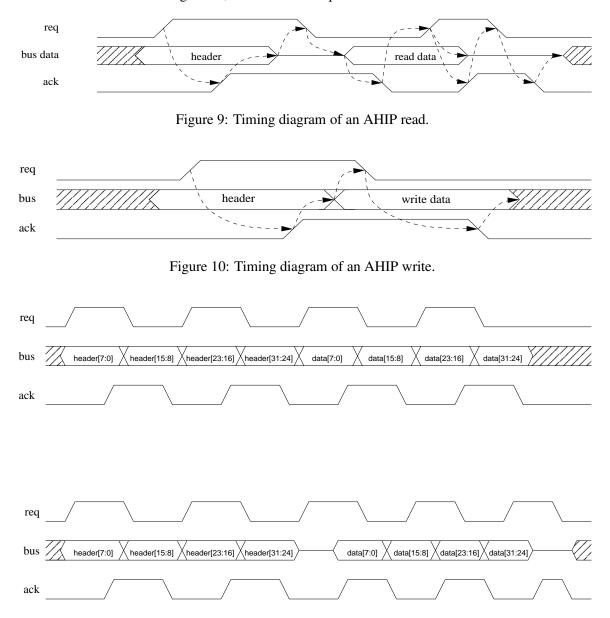

| 9  | Timing diagram of an AHIP read                                       |

| 10 | Timing diagram of an AHIP write                                      |

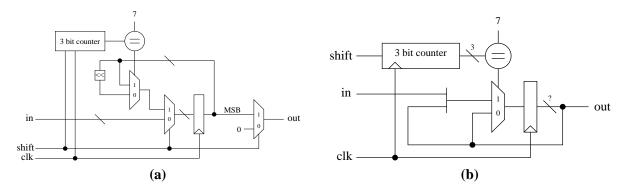

| 11 | Timing diagram of an 8 bit AHIP write and read                       |

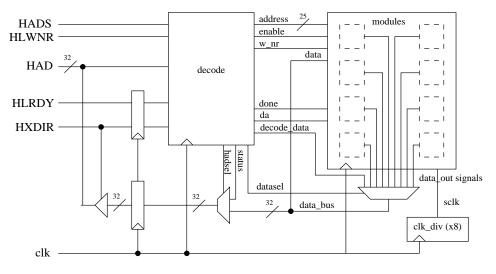

| 12 | Shift registers                                                      |

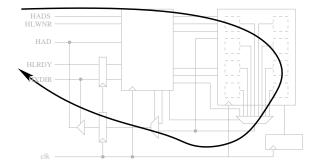

| 13 | Block diagram of the controller module                               |

| 14 | Dataflow through the controller                                      |

| 15 | Timing diagram of general PLX access                                 |

| 16 | Block diagram of the decode module                                   |

| 17 | Timing diagram of a write for decode module                          |

| 18 | Timing diagram of a read for decode module                           |

| 19 | Refresh timer for the SDRAM control module                           |

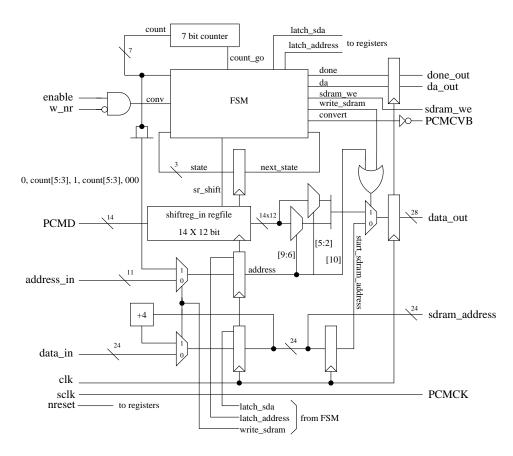

| 20 | Block diagram of the SDRAM control module                            |

| 21 | Timing diagram of SDRAM initialization                               |

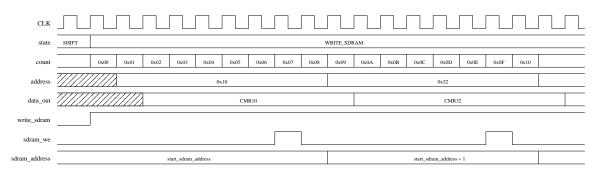

| 22 | Timing diagram of a SDRAM write                                      |

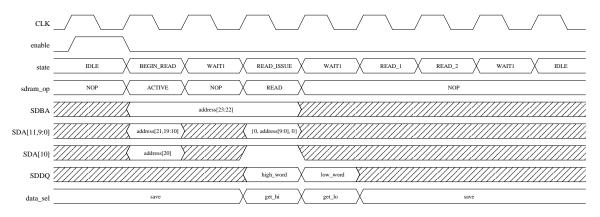

| 23 | Timing diagram of a SDRAM read                                       |

| 24 | Block diagram of the voltage set module                              |

| 25 | Timing diagram for the voltage set module                            |

| 26 | Block diagram of the voltage measure module                          |

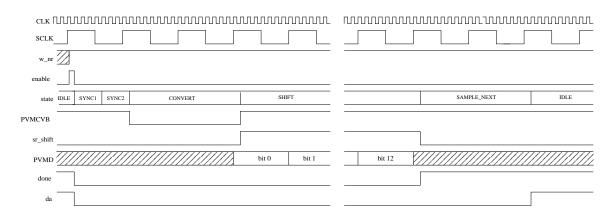

| 27 | Timing diagram for the voltage measure module                        |

| 28 | Block diagram of the current measure module                          |

| 29 | Timing diagram of the current measure module writing to SDRAM memory |

| 30 | Block diagram of the clock module                                    |

| 31 | Timing diagram for the clock module                                  |

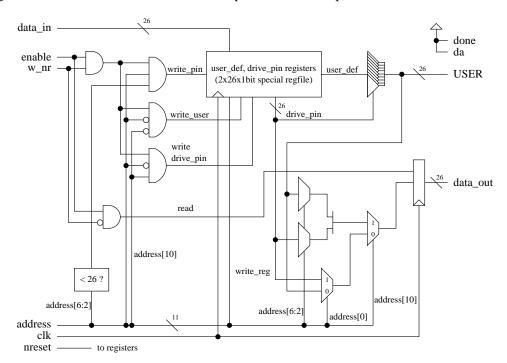

| 32 | Block diagram of the User pin control module                         |

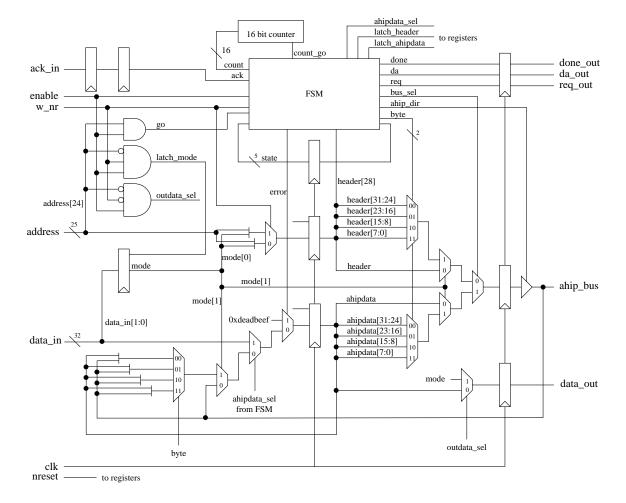

| 33 | Block diagram of the AHIP module                                     |

# List of Tables

| 1  | ATB0 Control Register                                | 9  |

|----|------------------------------------------------------|----|

| 2  | Frequency to M and N values conversion chart.        | 11 |

| 3  | Bit assignment of LGA_LED register.                  | 12 |

| 4  | Meaning of direction bits in the user pin registers. | 13 |

| 5  | AHIP modes.                                          | 13 |

| 6  | AHIP opcodes.                                        | 14 |

| 7  | Decode module wire descriptions.                     | 21 |

| 8  | Decode module state definitions.                     | 22 |

| 9  | Module numbers.                                      | 22 |

| 10 | SDRAM control module state definitions.              | 27 |

| 11 | SDRAM control module state transitions.              | 27 |

| 12 | SDRAM control module wire descriptions.              | 28 |

| 13 | Voltage set module state definitions.                | 30 |

| 14 | Voltage set module wire descriptions.                | 31 |

| 15 | Voltage measure module state definitions.            | 33 |

| 16 | Voltage measure module wire descriptions.            | 34 |

| 17 | Current measure module state definitions.            | 35 |

| 18 | Current measure module wire descriptions.            | 37 |

| 19 | Clock module state definitions                       | 39 |

| 20 | Clock module wire descriptions.                      | 40 |

| 21 | User pin control module wire descriptions.           | 42 |

| 22 | AHIP module wire descriptions.                       | 44 |

| 23 | AHIP module state definitions.                       | 45 |

| 24 | AHIP module state transitions.                       | 45 |

## **1** Introduction

This document is one in a set of three engineering documents describing the Assam Tester Baseboard Revision 0 (ATB0); this document describes the controller while the other two describe the actual hardware [1] and the software interface [2].

ATB0 is designed to provide a testbed for custom designed circuit boards that require multiple differing power supplies (referred to in this document as the "daughtercard"). ATB0 also provides a communication channel between a host PC and the daughtercard. To do so, ATB0 has the following devices:

- **Sixteen power supplies.** Each power supply can be configured to supply a voltage independently of each other; there are fourteen power supplies that supply a positive voltage between 0 and 4 volts and two that supply a negative voltage between 0 and -4 volts. The voltage of each of the positive power supplies can be read back to ensure proper operation; the current drawn from each positive power supply can also be read for power measurements.

- **Onboard SDRAM.** The onboard SDRAM is 12 bits wide and 64 MWs deep. Its primary purpose to provide temporary storage for power measurements allowing measurements to be performed quickly while testing and read back later, after testing is complete.

- **Frequency synthesizer.** The frequency synthesizer is used to provide a clock to the daugthercard and can be configured to run between 25 MHz and 400 Mhz.

- **60 I/O pins between ATB0 and the daughtercard.** 34 of these pins are used to perform reads and writes on the daughtercard using the AHIP protocol [3]. The remaining 26 are used as individual user defined I/O pins.

- Two LEDs. These can be used to provide status flags to the user.

The controller for ATB0 is written in Verilog for the Xilinx on ATB0. Its purpose is two-fold: 1) control the various devices on ATB0, and 2) facilitate communication between the host PC and the daughtercard. All communication between the host PC and the controller is in the form of reads and writes to memory locations. A PLX interface card is used to convey a read or write from the host PC to the controller.

Standard operation involves the user connecting a daughtercard to ATB0 then writing to memorymapped registers to configure the devices on ATB0 according to the requirements of the daughtercard. The user then performs some task by communicating with the daughtercard, either directly, by reading from or writing to the user pins, or using the AHIP interface. Tasks could include operations such as such as running an application on a synthesized CPU, performing memory operation on a memory controller, etc. While the task is being performed, certain events, as configured by the user, cause the controller to measure the current drawn from each of the power supplies and store those measurements in the onboard SDRAM chips. The user can later read those values from the SDRAM and analyze the power consumption over time of the task.

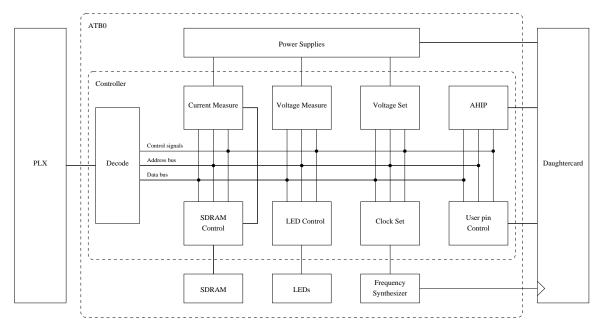

Figure 1 shows a block diagram of the system. A memory access operation from the host PC is conveyed by the PLX interface card to ATB0. A decode module in the controller receives the operation and decodes it. The decode module then drives the address and data onto the central buses and enables the appropriate module according to the nature of the operation. The voltage set and voltage measure modules communicate directly with the power supplies. The current measure module communicates with both the power supplies and the SDRAM control module to enable it to store current measurements into the onboard

memory. The SDRAM module can receive memory accesses from both the decode module and the current measure module and performs the access to the SDRAM. The AHIP module communicates with the daughtercard through dedicated AHIP pins and the user pin control module allows the user to set and read individual pins connected to the daughtercard. The LED control module drives the LEDs directly and the Clock set module communicates with the frequency synthesizer to provide the clock to the daughtercard.

Figure 1: Block diagram of ATB0.

## 2 User Interface

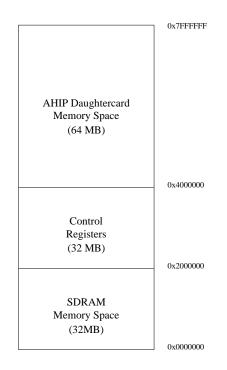

The user interacts with the controller by reading and writing to memory locations on the host PC. The PLX then forwards these requests to the baseboard and relays the response back to the user. The PLX allows addresses up to 28 bits wide and enforces word addressing by forcing the lower two bits to zero. The controller currently uses 27 of those bits, leaving the top half of possible memory space open for expansion. As shown in Figure 2, memory is divided into three main sections, SDRAM Memory, Control Registers, and AHIP Daughtercard Memory space.

Accessing memory in SDRAM is described in Section 2.1. Configuration of the devices using the control registers is described in Section 2.2. Finally, communicating with the daughtercard is described in Section 2.3.

## 2.1 Accessing SDRAM

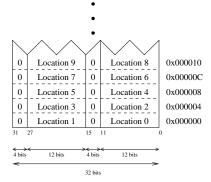

Each word in SDRAM memory space corresponds to two 12-bit values in the actual SDRAM; Figure 3 shows the resulting memory layout, relating SDRAM memory locations to addresses in SDRAM memory space. Since there are  $2^{24}$  locations in SDRAM,  $2^{23}$  four byte words, or 32 MBs, are needed to access all the SDRAM memory, thus the SDRAM memory space in the controller is 32 MBs. To access a word in SDRAM memory space, simply read from or write to the corresponding address in the ATB0 memory space.

Figure 2: ATB0 Memory Map. Address are relative to the bottom of ATB0 address space.

Figure 3: SDRAM memory layout. Addresses are relative to the bottom of SDRAM Memory space.

## 2.2 Configuration

Configuring ATB0 is accomplished by writing to a number of memory-mapped control registers. The address and functionality of each register is summarized in Table 1. Setting the voltage of the Power Supplies is described in Section 2.2.1. Measuring the current is described in Section 2.2.2. Calibrating the current measurements is described in Section 2.2.3. Setting the clock speed that the frequency synthesizer generates is described in Section 2.2.4. Finally, Section 2.2.5 show how to set refresh rate of the onboard SDRAM chips and the Logic Analyzer and LED outputs.

### 2.2.1 Setting the voltage

ATB0 is equipped with 16 user-controlled independent power supplies. The desired voltage of power supplies 0 -  $13^*$  can be set between 0V and  $4.095V^{\dagger}$ ; the actual voltage supplied and the current drawn from the power supply can be measured and read by the user. The desired voltage of power supplies 14 and 15 can be set between 0V and -4.095V but the actual voltage and current can not be measured. Note that the current that each supply is able to produce varies, see the hardware document [1] for more information.

Setting the desired voltage is accomplished by writing the appropriate register (VSR0 - VSR15) with the desired value. The registers are 12 bits wide (thus, only the lower 12 bits of the 32 bits written to the register are used) and their value corresponds linearly to the range of 0V to 4.095V. To convert from a desired voltage into a value to put in the register, divide the desired voltage by the maximum voltage ( $V_{REF}$ ) and multiply by the maximum value  $2^{12}$ -1 = 4095 as shown in Equation 1.

$$VSRn = \frac{volts}{V_{REF}} * (2^{12} - 1) \approx \frac{volts}{4.095} * 4095 = volts * 1000$$

(1)

This results in a coding that is about  $1 \frac{mV}{bit}$  since  $V_{REF}$  is about 4.095V and thus the voltage set register can be set to approximately 1000 times the desired voltage; however, if precision is necessary, the user should measure  $V_{REF}$  and use the actual value in the calculation. Writing to VSR0 - VSR14 will only set the register, it will not cause the power supply to output the desired voltage. Writing to VSR15 both sets VSR15 and causes all 16 power supplies to output the voltage that is contained in their corresponding register.

Once VSR15 is written to and the power supplies are set to the desired values, the actual voltage produced by each power supply can be obtained by simply reading the appropriate voltage measure register (VMR). This returns a 12-bit value that corresponds linearly to the range of 0V to 5V, which is the reference voltage supplied to the ADC used to measure the voltage. Thus, to obtain a voltage from the value read from the VMR, divide by the maximum value ( $2^{12}-1 = 4095$ ) and multiply by the ADC reference voltage ( $V_{REF\_ADC}$ ) as shown in Equation 2.  $V_{REF\_ADC}$  is approximately 5V, but like  $V_{REF}$ , the user should measure this if precision is required.

$$Volts = \frac{VMR}{2^{12} - 1} * V_{REF\_ADC} \approx \frac{VMR}{4095} * 5$$

<sup>(2)</sup>

<sup>\*</sup>Power supplies are numbered 0 - 15 to make it coincide more nicely with the addressing scheme; however, on the schematics, power supplies are numbered 1 - 16, this numbering scheme is not used anywhere but the schematic, don't let that confuse you.

<sup>&</sup>lt;sup>\*</sup>"4.095V [is] the theoretical maximum voltage. The actual voltage is limited by the dropout voltage of the regulators, with 3.9V the expected limit."[4] See the hardware document[1] for more information.

| Register      | Address            | Description                                                                                                                                                                                                                                                                                                                                  | Read         | Write        |

|---------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|

| VSn           | 0x21000n0          | Voltage Set Registers - The desired voltage for power supply <i>n</i> . Writing to VSR15 commits the voltages to the power supplies.                                                                                                                                                                                                         | $\checkmark$ | $\checkmark$ |

| VMn           | 0x22000 <i>n</i> 0 | Voltage Measure Registers - The actual voltage of Power<br>Supply <i>n</i> . A measurement is made each time one of these<br>registers is read.                                                                                                                                                                                              | $\checkmark$ |              |

| CM_BURST      | 0x2300000          | Current Measure Burst - Reading this register causes the current being drawn from each power supply specified in the CM_MASK register to be measured and placed in SDRAM memory. The address in SDRAM memory space of the first measurement is returned. Writing sets the address in SDRAM memory space where the next burst will be placed. | $\checkmark$ | $\checkmark$ |

| CM_MASK       | 0x2300004          | Current Measure Mask - Each of the lower 14 bits in this register correspondes to a power supply (bit 0 correspondes to Power Supply 0). When CM_BURST is read, each power supply whose bit in this register is 1 has its current measured. (Currently not supported)                                                                        | $\checkmark$ | $\checkmark$ |

| CMmn          | 0x2301 <i>mn</i> 0 | Current Measure Registers - The current being drawn from<br>Power Supplies $m$ and $n$ . A measurement is made each<br>time one of these registers is read.                                                                                                                                                                                  | $\checkmark$ |              |

| CLOCK         | 0x2400000          | Clock - Used to set the frequency generated by the on-<br>board frequency synthesizer.                                                                                                                                                                                                                                                       | $\checkmark$ | $\checkmark$ |

| SDRAM_RT      | 0x2500000          | SDRAM Refresh Timer - The number of clock ticks be-<br>tween each refresh of the SDRAM modules.                                                                                                                                                                                                                                              | $\checkmark$ | $\checkmark$ |

| USER_ALL      | 0x2600000          | All user pins - The logical values of all 26 user pins.                                                                                                                                                                                                                                                                                      |              |              |

| USER_DIR      | 0x2600004          | User pins direction - Whether all 26 user pins are set to<br>be input or output. A high bit indicates the controller is<br>driving that pin (an output).                                                                                                                                                                                     | $\checkmark$ | $\checkmark$ |

| USER <i>p</i> | 0x2601 <i>pp</i> 0 | User Pins - Reading returns the logical value of user pin $p$ and I/O direction. Writing a 0 or 1 sets the pin as output with the given value and writing a value of 2 resets the pin to be an input.                                                                                                                                        |              |              |

| LGA_LED       | 0x2000000          | LGA and LED outputs.                                                                                                                                                                                                                                                                                                                         |              |              |

| AHIP_MODE     | 0x2700000          | AHIP Mode. Used to allow for test and 8 bit modes.                                                                                                                                                                                                                                                                                           |              |              |

| STATUS        | 0x2800000          | Status flags                                                                                                                                                                                                                                                                                                                                 |              |              |

Table 1: ATB0 Control Registers. Addresses are relative to the bottom of the ATB0 address space.

| 31 28  | 27 16            | 15 12  | 11 0             |

|--------|------------------|--------|------------------|

| unused | Value for PS $m$ | unused | Value for PS $n$ |

| 4      | 12               | 4      | 12               |

Figure 4: Format of VMRmn.

#### 2.2.2 Measuring the current

The current drawn from a power supply can be measured either individually or as a burst with other power supplies. The current from two different power supply can be measured individually by reading from the appropriate Current Measure Register (CMmn). The current drawn from power supply m is returned in the top 16 bits, and the current drawn from power supply n is returns in the lower 16 bits as shown in Figure 4. The value returned for each supply is described in Section 2.2.3. To measure multiple power supplies in a single burst, first set the CM\_MASK register so that each power supply to be measured has a 1 in its bit within the mask. The CM\_BURST register can optionally be written to to specify where in SDRAM memory space to place the measurements. Reading the CM\_BURST register actually performs the measurements and returns the address in SDRAM memory space at which the first measurement was placed.

#### 2.2.3 Calibrating current measurement

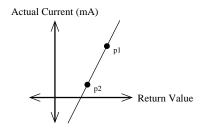

Because of hardware issues (see [1]), the current measured by the power supplies is not exactly the current that is being drawn from the power supply by the daughtercard; therefore, it is necessary to adjust the measurements recieved. To calibrate a power supply to determine how to adjust the measurements, load the power supply with two different loads and measure, with lab equipment, the actual current through each load, as well as the value returned by the controller by reading the Current Measure register. These two measurements define two points in a plane with the current on the y-axis and the return value on the x-axis. These two points define a line in that plane. That line defines the relationship between the value returned by the controller as the current measurement and the actual current being drawn by the daughtercard for a single power supply. Figure 5 shows this plane.

Figure 5: Calibrating the current. The y-axis is the measured current, the x-axis is the value returned by the controller as the current for that supply. p1 and p2 represent values obtained by placing different loads across the power supply. The line relates the value returned by measuring the current to the actual current drawn by the daughtercard.

Given the above calibration, basic geometry gives us an equation to convert a value returned by the controller to the actual current begin drawn by the daughter card. Equation 3 gives the slope of the line, Equation 4 gives the intercept. Using the slope and the intercept, Equation 5 is the equation needed. More

| 31  | 14  | 13 11 | 10 9 | 80 |

|-----|-----|-------|------|----|

| unu | sed | test  | Ν    | М  |

| 18  |     | 3     | 2    | 9  |

Figure 6: Clock register format.

| Frequency (MHz) | Ν | М             |

|-----------------|---|---------------|

| 25 - 50         | 3 | 8 * frequency |

| 50 - 100        | 2 | 4 * frequency |

| 100 - 200       | 1 | 2 * frequency |

| 200 - 400       | 0 | frequency     |

Table 2: Frequency to M and N values conversion chart.

representative names, ratio and offset, can be used for the slope and intercept respectively.

$$slope = \frac{(Measured_1 - Measured_2)}{CMR_1 - CMR_2}$$

(3)

$$intercept = Measured_2 - (slope * CMR_2)$$

(4)

$$current = (slope * CMR) + intercept = (ratio * CMR) + offset$$

(5)

### 2.2.4 Setting the generated clock speed

ATBO has a frequency synthesizer that is capable of creating clock signals in the range of 25 to 400 MHz; the frequency can be set up by writing to the CLOCK register whose format is shown in Figure 6. The used 14 bits of the register are split into three fields: test, N, and M. The test field is used to choose what test mode to put the frequency synthesizer in and should be set to 0 for normal operation. Table 2 provides values for N and M to achieve a desired frequency. Note that M should always be between 200 and 400. See the frequency synthesizer's datasheet [5] for more information on what these numbers mean and what test modes are available.

## 2.2.5 Other configuration registers

The STATUS register provides status for each of the modules within the controller and can be used for debugging purposes. As shown in Figure 7, bits 15 to 8 contain the da (data available) signal for each module and bits 7 to 0 contain the done signal for each module. The bits are ordered according to the module numbers in Table 9 (i.e. module 2's done signal is bit 2 and its da signal is bit 10). See the implementation section (Section 3) for more information on module numbers and what the da and done signals mean.

Using other configuration registers is mostly a matter of simply writing a value to the register. Each of the registers can also be read if necessary.

**SDRAM Refresh Timer** The SDRAM Refresh Timer register (SDRAM\_RT) contains the number of clock ticks between each refresh of the SDRAM modules and is independent of anything else. To change this timer simply write a new value to the register, and to check the currently value simply read it. The

|   | 31  | 16  | 15 | 8       | 7    | 0       |

|---|-----|-----|----|---------|------|---------|

|   | unu | sed | da | signals | done | signals |

| 1 | 16  |     |    | 8       |      | 8       |

Figure 7: Status register format.

| Bit #  | Signal |

|--------|--------|

| 0      | LED0   |

| 1      | LED1   |

| 2      | LGA0   |

| 3      | LGA1   |

| 4 - 31 | unused |

Table 3: Bit assignment of LGA\_LED register.

SDRAM documentation [6] states that the modules should be refreshed every  $15.625\mu$ s; the default value of 78 (0x4E) causes a refresh every  $15.6\mu$ s with a 5 MHz clock. If a 40 MHz clock is used, this value should be set to 625 (0x271) to achieve a refresh every  $15.625\mu$ s.

LGA and LED outputs The two LGA outputs go to a jumper on the back side of the baseboard such that they can be used as inputs to a logic analyzer. The LED outputs go to the two LEDs on the baseboard. All four of these outputs can be set using the LGA\_LED register with the bit assignments shown in Table 3.

## 2.3 Communication with the daughtercard

The controller allows the user to either manually communicate with the daughtercard using the user pins directly (Section 2.3.1), or read and write to the AHIP Daughtercard Memory area and have the controller take care of forwarding the data to the daughtercard, which it does using AHIP (Section 2.3.2).

## 2.3.1 Accessing the user pins

User pins can be accessed directly, either individually or collectively in parallel. The USERp registers allow access to an individual pin p. When a USERp register is read, bit 0 contains the logical value currently on the pin, whether it is being driven by the controller or the daughtercard, and bit 1 contains the I/O direction of the pin, a 1 indicates the pin is an output pin and being driven by the controller, a 0 indicates the pin is an input and being driven by the daughtercard (or floating) (as shown in Table 4). When a value of 0 or 1 is written to a USERp register, the controller will drive the pin at that value; if a value of 2 is written to a USERp register, the controller will stop driving the pin with any value, making it an input pin, available for the daughtercard to drive.

The USER\_ALL and USER\_DIR registers allow access to all 26 pins at once. Reading USER\_DIR returns wether each pin is set as an output or input, each pin's direction is in 1 bit (i.e. pin 0's direction is in bit 0). Writing to USER\_DIR sets the direction of all 26 pins according to the corresponding bit in the value written (i.e. if bit 5 of the value written is 1, pin 5 will be set to be an output). Reading the USER\_ALL register returns the value of all 26 pins in the low 26 bits of the result. Writing to USER\_ALL sets all *out put*

| Bit value Meaning                                                                                                                    |  |                                                                     |  |

|--------------------------------------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------------|--|

| <ul><li>0 Pin is an input and being driven by the daughterca</li><li>1 Pin is an output and being drive by the controller.</li></ul> |  | Pin is an input and being driven by the daughtercard (or floating). |  |

|                                                                                                                                      |  | Pin is an output and being drive by the controller.                 |  |

Table 4: Meaning of direction bits in the user pin registers.

| Mode       | Number | Description                                                   |

|------------|--------|---------------------------------------------------------------|

| Normal     | 0      | All reads and writes are normal 32 bit reads and writes.      |

| Test       | 1      | All writes are test writes, reads to address 0x0 are test ad- |

|            |        | dress reads, reads to any other address are test data reads.  |

| 8-bit      | 2      | All reads and writes are normal 8 bit reads and writes.       |

| 8-bit test | 3      | Like Test mode, but all 8 bit reads and writes.               |

Table 5: AHIP modes.

pins to the corresponding bit in the value written. Pins that are set to be input pins will not be affected by a write to USER\_ALL.

#### 2.3.2 Asynchronous Host Interface Port (AHIP)

AHIP is a data communication protocol that facilitates communication between two devices that do not share a common clock. The controller uses AHIP to allow the user to access memory space on the daughtercard directly. To read from or write to a memory location on the daughtercard, the user need only read from or write to the AHIP Daughtercard Memory space on ATB0. The controller performs the host side of AHIP and handles the actual transfer of data to and from the daughtercard, which acts as the slave.

AHIP can be used in one of four modes by setting the AHIP\_MODE register to a mode number shown in Table 5. When in normal mode, all reads and writes to AHIP Daughtercard memory space become normal AHIP reads and writes using the standard 32-bit AHIP protocol. When in test mode a write causes a test write, a read from daughtercard address zero causes a test address read and a read from any other daughtercard address causes a test data read, see Section 2.3.2.4 for more information on test mode. When in 8 bit mode, normal reads and writes are performed, but the 8-bit AHIP protocol (Section 2.3.2.3, which uses only the bottom 8 bits of the bus, is used. Finally, in 8 bit test mode, test reads and writes are performed the same as in test mode, but the 8-bit AHIP protocol is used.

The AHIP protocol is described below to facilitate creating a client for the daughtercard that can communicate with ATB0. An example client is included in the source directory (in the ahip\_client subdirectory) which is written to be connected to a block memory module on a Virtex II FPGA to create a simple memory system that can be written to and read from using AHIP. ahip\_client.v contains the ahip client module for normal 32 bit operation, and ahip8\_client.v contains an ahip client that uses an 8 bit bus. Another example can be found in ATC0 [3] which implements the client side of AHIP.

**2.3.2.1** Asynchronous Transaction Protocol The protocol uses a 32-bit wide bi-directional bus and two handshake signals, req, controlled by the host, and ack, controlled by the slave, to transfer data to and from the daughtercard, with the controller acting as the host and the daughtercard as the slave. When idle, both req and ack are low and the host is responsible for driving the bus so that it does not float. The host starts a transaction by raising the req signal and placing a header on the bus in the format shown in Figure 8. The

| 31  | 28  | 27 24 | 23      | 0 |

|-----|-----|-------|---------|---|

| opc | ode | bmc   | address |   |

| 4   | 4   | 4     | 2       | 4 |

Figure 8: AHIP Header format.

| Opcode | Function            |

|--------|---------------------|

| 0000   | Normal Write        |

| 0001   | Normal Read         |

| 1000   | Test Write          |

| 1001   | Test Read (Data)    |

| 1101   | Test Read (Address) |

Table 6: AHIP opcodes.

header contains three fields: a 4-bit opcode field; a 4-bit *burst-mode counter* (bmc) for burst-mode read and write; and a 24-bit address. The burst-mode read/write is not currently implemented by the controller and reserved for future implementations, so the bmc field is set to zero and should be ignored. Table 6 shows the different opcodes available. During normal operation, only the normal read and write are used. Some opcodes are used to perform a self-test of AHIP, as described in Section 2.3.2.4. A variation of the standard protocol that uses an 8-bit data bus is also supported and described in Section 2.3.2.3.

**2.3.2.2** Writing and reading with AHIP The host starts a write by placing the header on the bus and raising the req signal. After the slave observes that req is high, it reads the header word and raises the ack signal. After the host receives ack, it places the write data on the bus and lowers req. The slave reads the bus value and then lowers ack. The host will then free the data bus and both the host and the slave return to the idle state. Figure 10 shows the timing diagram of the transaction.

Similar to word write, the host starts a read by placing the header on the bus and raising the req signal. The slave will obtain the header and asserts ack. Once the host sees the ack, it frees the data bus and lowers req. Once the slave is ready with the data, it places the data on the bus and lowers ack. The host reads the data off the bus and raises req again, the slave then frees the data bus and raises ack. The host lowers req, followed by the slave lowering ack, and both return to an idle state. Figure 9 shows the timing diagram of the word read.

**2.3.2.3 8** bit reads and writes When used in an 8 bit mode, reads and writes still transfer 32 bits, but they do so 8 bits at a time. The protocol is similar, the host begins a transaction by placing the bottom 8 bits of the header (header[7:0]) onto the bus and raising the req signal. The slave observes that req is high, reads the data from the bus and raises the ack signal. The host places the next 8 bits of the header onto the bus and lowers req, which the slave reads and lowers ack. This process continues until all 4 bytes of the header have been transmitted, one byte per edge. When the slave acknowledges receiving the last byte of the header, if the access is a write, the host continues to send the data word, 1 byte at a time, starting from the bottom 8 bits (data[7:0]), in the same manner until all four bytes have been sent. If the access is a read, the host frees the bus and raises req to signal the slave can begin transmitting the read data back. The slave then transmits the read data back to the host, one byte at a time, in similar manner. When the host raises req to acknowledge receipt of the last byte, the slave raises ack one more time to indicate it it no longer

driving the bus and the protocol finishes just as it did with the 32 bit read. The timing diagram for both an 8 bit write and read is shown in Figure 11, the write is on top.

Figure 11: Timing diagram of an 8 bit AHIP write and read. The write is on top and the read is on the bottom.

**2.3.2.4 AHIP Self-Test** To verify the correctness of AHIP functionality, both in the controller and the implementation on the daughtercard, the top bit of the opcode is used to run AHIP in test mode. The daughtercard must implement AHIP test mode for the test modes to be useful. When in test mode, a slave device will store the address and the value written during a Test Write. A Test Read will then return either the stored address or the stored data. The host can thus verify that both the data and address are being

transmitted correctly by performing a Test Write then a Test Read on both the data and the address and checking that those values correspond to the data and address just written.

## **3** Implementation details

The ATB0 controller is written in Verilog and consists of the following interconnected modules.

- **Controller** The top level module. It instantiates all other modules, connects them together, divides the clock to provide a slower clock when needed, collects output from all the modules and pipelines it off the chip, and defines the external interface.

- **Decode** Responsible for decoding requests received from the host computer via the PLX interface and forwarding the request on to the correct module depending on the address.

Voltage set Controls the DACs which set the desired voltage on the power supplies.

Voltage measure Controls the ADCs which measure the actual voltage on the power supplies.

Current measure Controls the ADCs which measure the current drawn from the power supplies.

SDRAM control Provides an interface to the on board SDRAM.

**Clock** Interfaces with the frequency synthesizer.

User pin Sets and reads the user pins.

**AHIP** Performs the host side of AHIP to perform memory transactions with the daughtercard on behalf of the user.

LGALED A small module which holds the LGA\_LED register.

Figure 1 in the Introduction (Section 1) shows a block diagram of how these module interconnect with each other and the rest of the system. In some instances, more than one of the modules requires the same functionality, such as shifting the bits of a register onto a serial data line; in these cases, a seperate "helper" module is defined and instantiated in each module that requires that functionality. The helper modules are:

shiftreg\_out Shifts the bits of a register onto a serial data line.

shiftreg\_in Shifts bits into a register from a serial data line.

**counter** A simple counter with an enable signal.

## 3.1 Clocking

One of the signals sent from the PLX daughtercard is a clock that is used as a global clock for the entire controller; it is called CXCOE in the schematics (Chip Transmission Line Clock and Output Enable). A slightly skewed second clock, called HCLK (Host Clock) in the schematics, is also sent but never used in the current implementation of the controller. This global clock is laballed "clk" in the block diagrams in this section.

Multiple modules (voltage set, voltage measure, current measure, and clock) interact with on board components that can not run at the frequency of the global clock, thus a clock that is eight times slower is generated for these components. It is labelled "sclk" in the block diagrams.

#### 3.1.1 Syncing with the slow clock

The FSM's of the modules that interact with the on board components that require a slower clock must run at the speed of the global clock for communication with the host PC to work. It is therefore necessary to get in sync with the slow clock before communicating with the on board component. To avoid repetition, the process is described here.

When leaving the idle state, the FSM checks to see if the slow clock is low or high, if it is high it enters the SYNC1 state and waits for it to go low. Once the slow clock is low, it enters SYNC2 and waits for it to go high. It then moves onto the next state at the beginning of the slow clock's cycle. A timing diagram of this can be seen in Figure 25 which shows the timing for the voltage set module.

## 3.2 Helper modules

Because they are used in many of the main modules, the helper modules are described here first.

#### 3.2.1 Shift registers

The shift registers act like ordinary shift registers, except they only shift once every 8 clock cycles because every modules that uses them interacts with a device running on a slower clock. They both use a 3 bit counter to slow the shifting down. The size of the shift register is variable and determined by the module that instantiates it using Verilog parameters.

The shiftreg\_out has three inputs, an input value the width of the register, a shift signal, and a clock signal; it has one single bit output. When shift is low, the input is latched into the register on each positive edge of the clock, the counter is disabled, and the output is tied low. When shift goes high the counter is started and the output switches to the most significant bit of the register. The register maintains its value until the count reaches 7, at which point it shifts it contents left by one bit, shifting a 0 into the LSB. The process continues while shift is held high.

The shiftreg\_in has the same ports, except the input value is a single bit and the output value is the width of the register. The shift input is used as the enable signal to the counter. When the count equals 7, the input bit is shifted into the LSB of the register, otherwise the register remains unchanged. When shift is low, the counter does not count and thus never equals 7, so no shifting occurs.

Figure 12: (a) shiftreg\_out block diagram. (b) shiftreg\_in block diagram.

### 3.2.2 Counter

The counter is a variable width counter with an enable signal. The width is determined by the module that instantiates it using Verilog parameters. When enable is low, the count stays at zero. When enable is high the count increases by one each rising edge of the clock. The implementation is straightforward.

## **3.3** Controller module

The controller module is the top level module of the ATB0 controller. Its port are the interface with the PLX interface card as well as the rest of the components on the baseboard, meaning each port in the controller module is an actual pin on the FPGA. Figure 13 is a high level block diagram of the controller module and how it connects everything together. It does not show each module's control signals or the connections between the modules and the external components on the baseboard. Figure 14 illustrates the flow of data through the controller. A memory access request comes in to the controller through the HADS, HLWNR, and HAD signals, is decoded by the decoder and forwarded on to a specific module via the address, enable, w\_nr, and data lines. The address bus to the modules is 25 bits wide because the address space requires 27 bits to access and two of those bits are always zero due to word alignment. The modules perform the requested task and communicates with the decode module using the done and da (data available) signals. When the module is done performing its task, the data from the correct module is selected from the data outputs of all the modules using the datasel signal; hadsel then selects to output this data to HAD. The data is sent back to the PLX using the HLRDY, HXDIR, and HAD signals. These three signals are all registered before being sent to the PLX for speed. While the module is performing the task, hadsel allows the status lines from the decoder to be driven onto data\_bus and consequently onto HAD. The HXDIR signal is used to enable a tri-state driver which drives the data\_bus onto HAD. The protocol of using these signals is described in Section 3.4 when the decode module is described.

Figure 13: Block diagram of the controller module.

The controller also instantiates a clock divider which is used by many of the components on the baseboard. The clock divider is implemented using a single 3 bit register that increments by one each rising edge of the input clock. The top bit of the register is used as the slow output clock.

Figure 14: Dataflow through the controller.

## **3.4 Decode module**

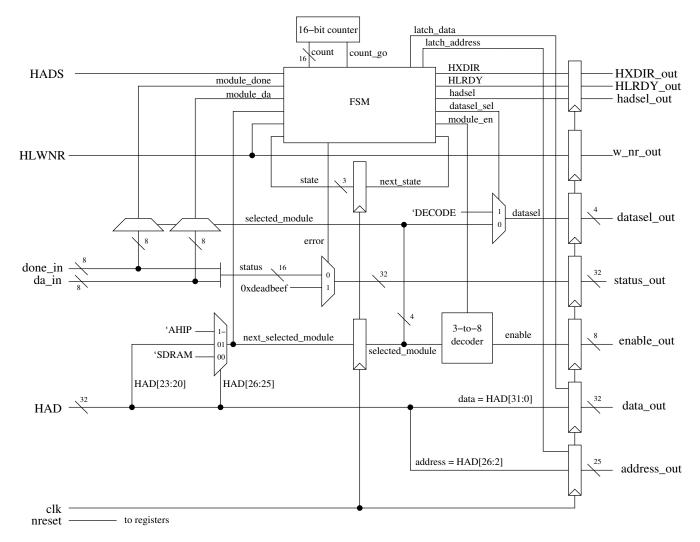

The decode module is responsible for communicating with the PLX interface card and controlling all other modules. Inputs from the PLX interface are HADS (Host Address/Data Strobe), HLWNR (Host Local Write Not Read), and HAD (Host Adress Data bus). The module also receives a done signal and a da (data available) signal from each module in the controller. There are two outputs to the PLX, HXDIR (Host Transmission Direction), and HLRDY (Host Local Ready). Control signals to each module are a w\_nr (write not read) and enable signal. The module has a data output to drive the data bus with and an address bus that goes to each module. Section 3.4.1 describes the PLX interface and Section 3.4.2 describes how the module operates.

## 3.4.1 PLX Interface

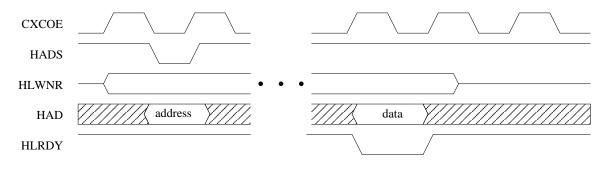

The controller is designed to receive memory access commands from a PLX interface card, with the PLX the bus master and the controller the bus slave. The protocol uses a 32-bit multiplexed address/data bus (HAD), an address/data strobe signal (HADS), a write/read signal (HLWNR), and a ready signal (HLRDY). The PLX begins a transaction by driving HAD with an address, setting HLWNR appropriately, and dropping HADS. This sends the address to the controller. The PLX then waits for the controller to drop HLRDY. If the operation is a write, when the controller drops HLRDY the PLX drives HAD with the write data until HLRDY goes high again. If the operation is a read, when the controller drops HLRDY the controller drives HAD with the read data for the PLX to read. Waiting for the HLRDY signal to drop allows the controller to delay the read or write until it is ready. Figure 15 shows the timing of the transaction.

Figure 15: Timing diagram of general PLX access.

### 3.4.2 Decode implementation

The decode module is one of the more complex modules in the controller. It is responsible for communicating with the PLX and controlling all other modules. Figure 16 shows a block diagram of the control module, with Table 7 providing an alphabetized description of each wire. At the heart of the module, like most of the modules in the controller, is an FSM which performs each step necessary during a read or a write. Table 8 shows each state with its output.

Figure 16: Block diagram of the decode module.

The module processes memory accesses from the PLX as they arrive. An access is initiated when the FSM is idle and the HADS signal is dropped. If HADS is dropped and the FSM is not idle, it is ignored. When the HADS signal is dropped the FSM raises the latch\_address signal to latch the address to the address\_out bus and examines the address to determine which module should handle the access. To do this, each module is given a number from 0 to 7 as shown in Table 9. If the address is in the SDRAM or AHIP memory spaces, the appropriate module is saved in the selected\_module register. If the address is in the control register space, bits 20 to 23 of the address are used as the selected module, this work because the

| Signal          | Description                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| address         | Output to modules. Used to drive the address bus that goes to each module.                                                                                                                                                                                                                                                                                                                                  |

| clk             | Global clock. Used as clock input to all registers.                                                                                                                                                                                                                                                                                                                                                         |

| count           | Input to FSM. 16-bit count. Incremented by one each clock period when count_go is high.                                                                                                                                                                                                                                                                                                                     |

| count_go        | Output from FSM. Instructs the counter to count.                                                                                                                                                                                                                                                                                                                                                            |

| cs_address      | Input from current measure module. Address to drive the address bus with when the current measure module is writing directly to the SDRAM.                                                                                                                                                                                                                                                                  |

| cs_we           | Input from current measure module. Used to drive the address from the current measure module onto the address bus instead of the address from the PLX. The only signal not from the FSM.                                                                                                                                                                                                                    |

| da_in           | Input from modules. One signal from each module indicates wheter or not the data supplied by the module is available or not.                                                                                                                                                                                                                                                                                |

| data            | Output to modules. Used to drive the data_bus when datasel is DECODE.                                                                                                                                                                                                                                                                                                                                       |

| datasel_sel     | Output from FSM. This determine whether the datasel_out output is hardwired to DECODE or is driven with the selected_module register.                                                                                                                                                                                                                                                                       |

| done_in         | Input from modules. One signal from each module indicates whether or not that module is in an idle state. (i.e. done with a transaction).                                                                                                                                                                                                                                                                   |

| enable          | Output to modules. One signal to each module which enable that module.                                                                                                                                                                                                                                                                                                                                      |

| error           | Output from FSM. This is used to drive the status bus with the value 0xdeadbeef.                                                                                                                                                                                                                                                                                                                            |

| HAD             | Input from PLX. Mulitplexed bus that carries both the address and data from the PLX.                                                                                                                                                                                                                                                                                                                        |

| HADS            | Input from the PLX. Used to initiate a memory access.                                                                                                                                                                                                                                                                                                                                                       |

| hadsel          | Output to main controller module. Used to determine if the data bus or the status signal should be driven to HAD on a read. High means the status is driven.                                                                                                                                                                                                                                                |

| HLRDY           | Output to PLX. Used to signal to the PLX that the controller is ready to either send or receive data. When this is low, the data on the bus is valid.                                                                                                                                                                                                                                                       |

| HLWNR           | Input from the PLX. Used to determine if memory access is a read or a write.                                                                                                                                                                                                                                                                                                                                |

| HXDIR           | Output to PLX. Used to determine if the controller of the PLX should drive the HAD bus.<br>High means the controller is driving the bus.                                                                                                                                                                                                                                                                    |

| latch_address   | Output from FSM. The enable signal for the address_out register. When high, address_out latches the address portion of the HAD bus. This is also the enable signal for the selected_module register.                                                                                                                                                                                                        |

| latch_data      | The enable signal for the data_out register. When high the data_out register latches the HAD bus.                                                                                                                                                                                                                                                                                                           |

| module_da       | Input to FSM. One of the da_in signals selected by selected_module.                                                                                                                                                                                                                                                                                                                                         |

| module_done     | Input to FSM. One of the done_in signal selected by selected_module.                                                                                                                                                                                                                                                                                                                                        |

| module_en       | This is used to enable the currently selected module. When high, the enable signal going to the module saved in the selected_module register is driven high.                                                                                                                                                                                                                                                |

| nreset          | Global reset. Used to reset all register.                                                                                                                                                                                                                                                                                                                                                                   |

| selected_module | An internal register. Contains the module number of the most recent access from the PLX. It determines this using the address on the HAD bus. If the address is in the SDRAM memory space or AHIP memory space it is the number corresponding to those modules, if the address is in the control register space, it obtains the module number from the address itself. Enabled by the latch_address signal. |

| status          | A status word to send back to the user. Contains all the done and da signals from the modules.                                                                                                                                                                                                                                                                                                              |

| w_nr            | Output to the modules. The HLWNR signal is simply forwarded to each module to indicate whether the access is a write or a read.                                                                                                                                                                                                                                                                             |

Table 7: Decode module wire descriptions.

#### ATB0 Engineering Document - Controller

|            | latch en   | ables   |             |        |       |       |            |          |       |            |

|------------|------------|---------|-------------|--------|-------|-------|------------|----------|-------|------------|

| state      | data       | address | datasel_sel | hadsel | HLRDY | HXDIR | module_en  | count_go | error | next_state |

| IDLE       | 0          | !HADS   | 1           | 1      | 1     | 1     | 0          | 0        | 0     | [1]        |

| WAIT_START | 0          | 0       | 1           | 1      | 1     | 1     | 0          | 1        | 0     | [2]        |

| WRITE      | 0          | 0       | 1           | 1      | 0     | 1     | 0          | 0        | 0     | WAIT_WRITE |

| WAIT_WRITE | count == 1 | 0       | 1           | 1      | 1     | 1     | count == 1 | 1        | 0     | [3]        |

| READ       | 0          | 0       | 0           | 0      | 1     | 0     | 1          | 0        | 0     | STALL      |

| STALL      | 0          | 0       | 0           | 0      | 1     | 0     | 0          | 0        | 0     | WAIT_READ  |

| WAIT_READ  | 0          | 0       | 0           | 0      | 1     | 0     | 0          | 1        | 0     | [4]        |

| SEND       | 0          | 0       | 0           | [5]    | 0     | 0     | 0          | 0        | 0     | IDLE       |

| TIMEOUT    | 0          | 0       | 0           | HLWNR  | 0     | HLWNR | 0          | 0        | 1     | IDLE       |

[1] next\_state = HADS ? IDLE : (next\_selected\_module == DECODE) ? SEND : WAIT\_START

[2] next\_state = module\_done ? HLWNR ? WRITE : READ :

(count = timeout) ? TIMEOUT : WAIT\_START

[3] next\_state = count == 1 ? IDLE : WAIT\_WRITE

[4] next\_state = module\_da ? SEND :

(count == timeout) ? TIMEOUT : WAIT\_READ

[5] hadsel = (selected\_module == DECODE)

Table 8: Decode module state definitions.

| Module          | Number |

|-----------------|--------|

| Voltage Set     | 0      |

| Voltage Measure | 1      |

| Current EMasure | 2      |

| Clock           | 3      |

| SDRAM           | 4      |

| USER pin        | 5      |

| LGALED          | 6      |

| AHIP            | 7      |

| DECODE          | 8      |

Table 9: Module numbers.

control registers are placed in memory such that bits 20 to 23 of the address contain the module number. If the selected module is the decode module, the FSM goes straight to the SEND state to send the status word. Otherwise it goes to the WAIT\_START state.

In the WAIT\_START state, the FSM waits for the selected module to raise its done signal in case the module is busy finishing a previous operation. During this state the counter is going and if the count reaches a specified timeout (currently 0xFFF) the FSM goes to the TIMEOUT state. When the selected module's done signal is high, the FSM goes to either the WRITE or READ state depending on the value of HLWNR.

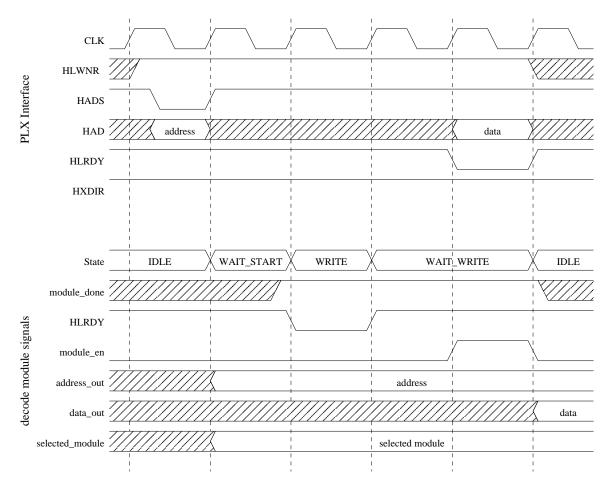

In the WRITE state, the FSM drops the HLRDY signal for one cycle and moves immediately to the WAIT\_WRITE state. Here it waits one cycle for the HLRDY signal to make it off the baseboard and to the PLX (it must go through two registers). In the second cycle in the WAIT\_WRITE state the latch\_data signal is raised to latch the data from the PLX and module\_en signal is raised to enable the selected module. Following the second cycle in the WAIT\_WRITE state, the FSM goes back to IDLE ready to process another request while the module that just received the write command is processing the write. Figure 17 shows a timing diagram of this process.

Figure 17: Timing diagram of a write for decode module.

#### ATB0 Engineering Document - Controller

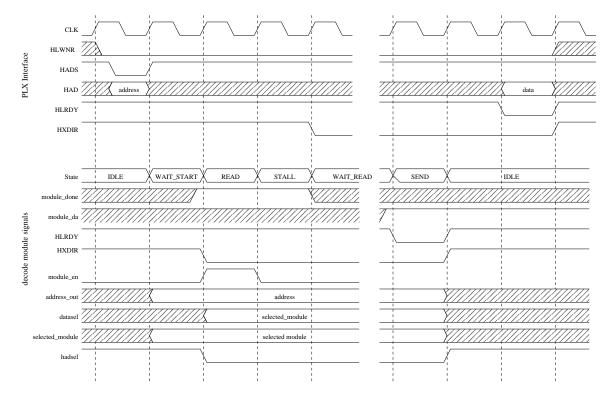

During the READ state, the module\_en signal is raised, enabling the selected module. The FSM then waits a cycle in the STALL state to give the module enough time to lower its da signal and for that da signal to make it back to the decoder. After waiting a cycle the FSM enters the WAIT\_READ state in which it waits for the module to raise its da signal to indicate that the read data is available. Like the WAIT\_START state, this state is timed by the counter and can timeout. Once the module raises its da signal, the FSM moves to the SEND state. In the SEND state, HXDIR is lowered to make the HAD bus driven by the controller and the HLRDY signal is lowered to tell the PLX the data is being sent on the bus. If the selected module is the decode module, hadsel is used to send the status word, otherwise the data bus, which is the output from the currently selected module, is sent to the PLX. After the SEND state the FSM goes back to IDLE. Figure 18 shows a timing diagram of this process.

Figure 18: Timing diagram of a read for decode module.

In the TIMEOUT state, HLRDY is dropped so the PLX will stop waiting for the controller. If the access is a read, the hadsel and error signal are used to return 0xdeadbeef. If the access is a write, the write is never performed. Following the TIMEOUT state the controller returns to IDLE.

## 3.5 SDRAM control module

The SDRAM control module is responsible for all communication with the SDRAM chips on the baseboard. The SDRAM chips need to be regularly refreshed so the module uses a seperate refresh timer to keep track of when a refresh should occur, this is described in Section 3.5.1 then the operation of the actual SDRAM control module is described in Section 3.5.2.

#### 3.5.1 Refresh Timer

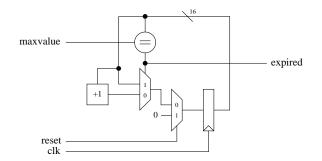

The refresh timer has three main inputs, a clock, reset, and maximum value, and one output, an expired signal. It consists of a simple counter that counts up by one each clock cycle until the count equals the maximum value given. When the count reaches the maximum value it stops counting and raises the expired output. It holds expired high until the reset signal is raised at which point it resets the counter to 0, and starts over. A block diagram is shown in Figure 19.

Figure 19: Refresh timer for the SDRAM control module.

## 3.5.2 SDRAM control module implementation.

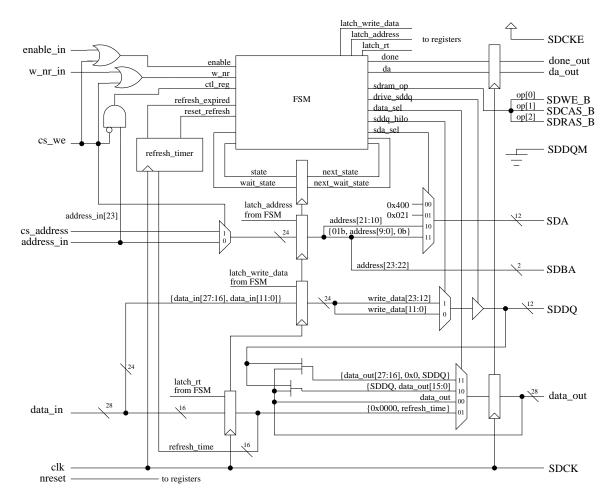

The SDRAM control module performs the necessary initialization of the SDRAM chips when reset and performs reads and writes to the SDRAM during use. Along with the standard interface to the decode module, the SDRAM control modules controls all signals going to the SDRAM chips. The global clock is used as the clock for the SDRAM chips and the CKE (clock enable) input to the SDRAM is tied high so the clock is always activated. The input/output mask, SDDQM, to the SDRAM is tied low so SDDQ is never masked. The three command inputs, SDWE\_B, SDCAS\_B, and SDRAS\_B, are controlled by the FSM within the SDRAM control module. The bank address (SDBA), address (SDA), and data (SDDQ) inputs to the SDRAM come from internal registers, as controlled by the FSM.

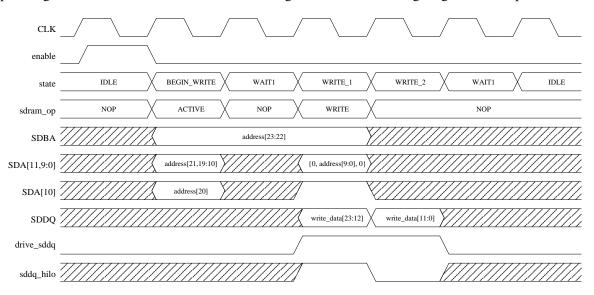

Figure 20 shows a block diagram of the SDRAM control module, with Table 12 providing an alphabetized description of each wire. Table 10 shows each state with its output. Because it is often necessary to wait a specific number of cycles, three WAIT states are defined in the FSM and an additional wait\_state register is added. When in the wait states, the FSM counts down from WAIT3 to WAIT2 to WAIT1 then returns to the state saved in the the wait\_state register.

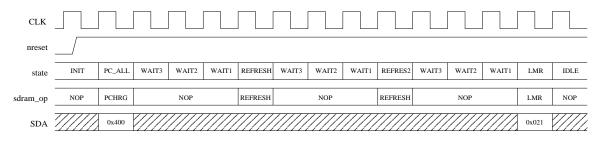

After a reset, the FSM goes through an initialization process to prepare the SDRAM chips for use, this follows the process described in the SDRAM data sheets [6]. After issuing an initial NOP command in the INIT state, in the PRECHARGE\_ALL state, sda\_sel is set to precharge\_all (00b) to output the address 0x400 to indicate the SDRAM should precharge all banks, a PRECHARGE command is then issued to the SDRAM. The FSM waits three cycles to ensure all banks are precharged then issues two REFRESH commands with a 3 cycle delay after each. Finally, a LMR command is issued loading the mode register with the value of 0x021 by setting sda\_sel to mode (01b). This tells the SDRAM that the controller wants sequential bursts of length two and a CAS latency of two (this means that data appears two cycles after a read command is issued). After the mode register is loaded, the FSM goes to an IDLE state. Figure 21 shows a timing diagram of this process.

When idle, the FSM waits for a memory access to come from ether the decode module or the current

Figure 20: Block diagram of the SDRAM control module.

Figure 21: Timing diagram of SDRAM initialization.

|               |           |          |               | latch      | n enabl | es      |           |            |      |      |

|---------------|-----------|----------|---------------|------------|---------|---------|-----------|------------|------|------|

| state         | sdram_op  | data_sel | sda_sel       | write_data | rt      | address | sddq_hilo | drive_sddq | da   | done |

| INIT          | NOP       | -        | -             | 0          | 0       | 0       | -         | 0          | 0    | 0    |

| PRECHARGE_ALL | PRECHARGE | -        | precharge_all | 0          | 0       | 0       | -         | 0          | 0    | 0    |

| INIT_REFRESH  | REFRESH   | -        | -             | 0          | 0       | 0       | -         | 0          | 0    | 0    |

| INIT_REFRESH2 | REFRESH   | -        | -             | 0          | 0       | 0       | -         | 0          | 0    | 0    |

| INIT_LMR      | LMR       | -        | mode          | 0          | 0       | 0       | -         | 0          | 0    | 0    |

| IDLE          | [1]       | [2]      | -             | [3]        | [4]     | [3]     | -         | 0          | ![3] | ![3] |

| BEGIN_WRITE   | ACTIVE    | save     | row           | 0          | 0       | 0       | -         | 0          | 1    | 0    |

| WRITE_1       | WRITE     | save     | column        | 0          | 0       | 0       | 1         | 1          | 1    | 0    |

| WRITE_2       | NOP       | save     | -             | 0          | 0       | 0       | 0         | 1          | 1    | 0    |

| BEGIN_READ    | ACTIVE    | save     | row           | 0          | 0       | 0       | -         | 0          | 0    | 0    |

| READ_ISSUE    | READ      | save     | column        | 0          | 0       | 0       | -         | 0          | 0    | 0    |

| READ_1        | NOP       | get_hi   | -             | 0          | 0       | 0       | -         | 0          | 0    | 0    |

| READ_2        | NOP       | get_lo   | -             | 0          | 0       | 0       | -         | 0          | 1    | 1    |

| WAIT3         | NOP       | save     | -             | 0          | 0       | 0       | -         | 0          | 0    | 0    |

| WAIT2         | NOP       | save     | -             | 0          | 0       | 0       | -         | 0          | 0    | 0    |

| WAIT1         | NOP       | save     | -             | 0          | 0       | 0       | -         | 0          | 0    | 0    |

[1] sdram\_op = refresh\_expired ? REFRESH : NOP

[2] data\_sel = (enable & ctl\_reg & !w\_nr) ? rt : save

[3] latch\_write\_data, latch\_address, !da, !done = (enable & !ctl\_reg)

[4] latch\_rt = (enable & ctl\_reg & w\_nr)

Table 10: SDRAM control module state definitions.

| State         | Next State    | Next Wait State |

|---------------|---------------|-----------------|

| INIT          | PRECHARGE_ALL | -               |

| PRECHARGE_ALL | WAIT3         | INIT_REFRESH    |

| INIT_REFRESH  | WAIT3         | INIT_REFRESH2   |

| INIT_REFRESH2 | WAIT3         | INIT_LMR        |

| INIT_LMR      | IDLE          | -               |

| IDLE          | [1]           | -               |

| BEGIN_WRITE   | WAIT1         | WRITE_1         |

| WRITE_1       | WRITE_2       | -               |

| WRITE_2       | WAIT1         | IDLE            |

| BEGIN_READ    | WAIT1         | READ_ISSUE      |

| READ_ISSUE    | WAIT1         | READ_1          |

| READ_1        | READ_2        | -               |

| READ_2        | WAIT1         | IDLE            |

| WAIT3         | WAIT2         | wait_state      |

| WAIT2         | WAIT1         | wait_state      |

| WAIT1         | wait_state    | -               |

[1] next\_state = (enable & !refresh\_expired & !ctl\_reg) ? (w\_nr ? BEGIN\_WRITE : BEGIN\_READ) : IDLE

Table 11: SDRAM control module state transitions.

| address Th<br>dre<br>address_in Inp | escription<br>his is the last saved address and is split into the three parts: address[23:22] is the bank, ad-<br>ess[21:10] is the row, and address[9:0] is the column. |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dre<br>address_in Inp               |                                                                                                                                                                          |

| address_in Inp                      |                                                                                                                                                                          |

| -                                   | put from the decode module, this is saved (latched) as address whenever latch_address is high and                                                                        |

|                                     | _we is low.                                                                                                                                                              |

| clk Gl                              | lobal clock. Used as clock input to all registers and sent to the SDRAM as SDCK.                                                                                         |

|                                     | put from current measure module. Address to write to when cs_we goes high.                                                                                               |

|                                     | put from current measure module. Indicates that the current measure module wants to write what                                                                           |

|                                     | on the data bus to cs_address.                                                                                                                                           |

|                                     | sed to determine if an access is reading or writing to a control register (namely, the refresh time) or                                                                  |

|                                     | tual SDRAM memory.                                                                                                                                                       |

|                                     | utput to decode module. Indicates when data_out is valid.                                                                                                                |

|                                     | put from decode module. Value to write to the SDRAM or set the refresh time to.                                                                                          |

| -                                   | utput to PLX. Contains either the latest value read from SDRAM or the value of the refresh time.                                                                         |

|                                     | ternal control signal. Used to determine what value is latched into data out. There are four choices:                                                                    |

|                                     | e refresh time, keep the same value, keep the low 16 bits and get the high 16 bits from SDDQ, or                                                                         |

|                                     | ep the high 16 bits and get the low 16 bits from SDDQ.                                                                                                                   |