# A Unified Compiler Backend for Distributed, Cooperative Heterogeneous Execution

by

Jessica Morgan Ray

B.S., University of Massachusetts Amherst (2012)

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Science in Computer Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2018

| ( | $\overline{z}$ | Massachusetts | Institute of | Technology | 2018. | All rights | reserved. |

|---|----------------|---------------|--------------|------------|-------|------------|-----------|

|   |                |               |              |            |       |            |           |

| Author      |                                                           |

|-------------|-----------------------------------------------------------|

|             | Department of Electrical Engineering and Computer Science |

|             | January 31, 2018                                          |

| Certified 1 | by                                                        |

|             | Saman Amarasinghe                                         |

|             | Professor of Electrical Engineering and Computer Science  |

|             | Thesis Supervisor                                         |

| Accepted    | by                                                        |

|             | Leslie A. Kolodziejski                                    |

|             | Professor of Electrical Engineering and Computer Science  |

|             | Chairwoman, Department Committee on Graduate Students     |

# A Unified Compiler Backend for Distributed, Cooperative Heterogeneous Execution

by

Jessica Morgan Ray

Submitted to the Department of Electrical Engineering and Computer Science on January 31, 2018, in partial fulfillment of the requirements for the degree of Master of Science in Computer Science

#### Abstract

In many of today's applications, achieving high-performance is critical. Numerous architectures, such as shared memory systems, distributed memory systems, and heteregeneous systems, are all used in high-performance computing. However, all of these have different optimizations and programming models. Additionally, performance is not always portable across architectures—one optimization that provides significant improvement in one system may have little to no effect in another system.

Writing high-performance code is a notoriously difficult task that requires significant trial-and-error. Writing high-performance code for multiple architectures is even harder, particularly when these architectural components are all together in a single heterogeneous system and the programmer has to make them all cooperate in order to achieve the highest performance. Hand-optimization only goes so far; it is infeasible to try many compositions of optimizations by hand, so the resulting performance will likely be sub-optimal. This thesis employs a scheduling language approach to abstract optimizations and code generation for shared memory with NUMA multicore, distributed memory, and GPU systems. To the best of our knowledge, we provide the first scheduling language approach that lets a programmer schedule cooperative execution on distributed, heterogeneous systems, all from a single algorithm. Our work extends an existing mid-level compiler, TIRAMISU, with several primitives and functions that present the programmer with a unified interface for generating code for several backends and execution configurations.

Our results show that we are able to generate efficient MPI code and CUDA code for distributed memory and heterogeneous GPU systems from a single algorithm. From our unified scheduling abstraction, we are able to generate distributed, heterogeneous cooperative code, giving us OpenMP+MPI+CUDA capability without the extra complexities that come with using multiple programming models.

Thesis Supervisor: Saman Amarasinghe

Title: Professor of Electrical Engineering and Computer Science

### Acknowledgments

In 2015, an MIT professor took a gamble on an incoming grad student who was interested in performance engineering and compilers. That student was worried that her lack of experience in those areas would be cause for concern, but that professor reassured her that she would learn everything she needed to along the way, and he took her as one his students. Of course, that student was me and that professor was (and is!) my fantastic advisor Saman Amarasinghe. There is no way I could've learned all I did over the past few years and do the work for this thesis without Saman's insight and guidance. Every step of the way, throughout the numerous project changes, dead ends, frustrations, and thankfully, the achievements, Saman has been there. I'm extremely grateful to have an advisor that genuinely cares about the progress of his graduate students. Thank you Saman–I'm very excited for the PhD adventure over the next \*few\* years!

Secondly, I want to thank the postdoc in my group, Riyadh Baghdadi. He is the author of TIRAMISU, the compiler that this thesis builds from. He provided endless guidance and knowledge to me on TIRAMISU, ISL, and Halide, and was there to answer all of my questions. This work would not have been possible without him!

I have a lot of individuals from MIT Lincoln Laboratory that I owe many thanks to as well. First off, I'm humbled by my acceptance into the Lincoln Scholars Program (LSP), and I want to thank the entire LSP committee for giving me this opportunity. It was difficult for me originally to leave a great place like MITLL when I went to grad school, so being able to come back through LSP is amazing. I'm looking forward to what the future brings me at MITLL! I also owe thanks to my group leaders at MITLL, Dr. Nick Malyska and Dr. Joe Campbell, for their help in preparing my LSP application, as well as for the opportunities they have provided for me during my time at MITLL. Additionally, thanks to Dr. Doug Sturim, Dr. Elizabeth Godoy, and Elizabeth Salesky from my group at MITLL for all their help in preparing my application (for both LSP and also grad school), and just helping me keep my sanity in general!

Of course, I can't forget to thank one of my professors from UMass, Professor Hanna Wallach. She has helped me with everything from getting me into MITLL to writing recommendations for my grad school applications, and even my LSP application.

Thanks to my amazing friend Whitney for answering my numerous questions about LSP, sympathizing with me over thesis struggles, cooking me dinner when I started getting stressed, and keeping me laughing throughout the whole process.

Obviously, thanks to all my friends for keeping me sane throughout! You all are the best friends I could have asked for!

And thanks to my wonderful boyfriend David. Your constant motivation and patience was more helpful in getting me through this process than I could ever put into words. I'm looking forward to endless hours of watching Family Guy and Game of Thrones with you once this thesis is done:)

Finally, how do I even begin to thank my parents? My parents have always been incredibly supportive through all of my endeavors, and I'm so lucky to have them. They've always been there for me to keep me positive even when I felt like giving up, and I often look to them as the voice of reason when it seems like everything is getting out of hand. Thank you for the unconditional love and support you've provided to me my whole life. Also thank you for letting me bring my laundry home almost every weekend.

# Contents

| 1        | Intr | oducti  | ion                                       | 15         |

|----------|------|---------|-------------------------------------------|------------|

|          |      | 1.0.1   | A Motivating Example                      | 18         |

| <b>2</b> | Sys  | tem A   | rchitecture Background                    | <b>2</b> 5 |

|          | 2.1  | Shared  | d Memory Systems                          | 25         |

|          |      | 2.1.1   | Architecture and Execution Overview       | 25         |

|          |      | 2.1.2   | High Performance Shared Memory Code       | 30         |

|          |      | 2.1.3   | Limitations of Shared Memory Systems      | 36         |

|          | 2.2  | Distril | buted Memory Systems                      | 37         |

|          |      | 2.2.1   | Architecture and Execution Overview       | 37         |

|          |      | 2.2.2   | High Performance Distributed Memory Code  | 38         |

|          |      | 2.2.3   | Limitations of Distributed Memory Systems | 46         |

|          | 2.3  | Graph   | ics Processing Units (GPUs)               | 48         |

|          |      | 2.3.1   | Architecture and Execution Overview       | 49         |

|          |      | 2.3.2   | High Performance GPU Code                 | 52         |

|          |      | 2.3.3   | Limitations of GPUs                       | 60         |

| 3        | The  | TIRA    | MISU Compiler                             | 63         |

|          | 3.1  | The P   | olyhedral Model                           | 63         |

|          |      | 3.1.1   | Overview                                  | 63         |

|          |      | 3.1.2   | Code Generation from the Polyhedral Model | 67         |

|          | 3.2  | TIRAN   | MISU                                      | 68         |

|          |      | 3.2.1   | Layer I: Abstract Computation Layer       | 69         |

|   |                | 3.2.2   | Layer II: Computation Placement Layer                 | 70 |

|---|----------------|---------|-------------------------------------------------------|----|

|   |                | 3.2.3   | Layer III: Concrete Computation Layer                 | 71 |

|   |                | 3.2.4   | Scheduling Language                                   | 71 |

|   |                | 3.2.5   | Code Generation in TIRAMISU                           | 71 |

| 4 | Dis            | tribute | ed, Heterogeneous, and Cooperative Code Generation    | 73 |

|   | 4.1            | Sched   | uling for Distributed, GPU, and Cooperative Execution | 73 |

|   |                | 4.1.1   | Distributed                                           | 74 |

|   |                | 4.1.2   | GPU                                                   | 75 |

|   |                | 4.1.3   | Data Transfers                                        | 77 |

|   | 4.2            | Data    | Layout                                                | 81 |

|   | 4.3            | Code    | Generation                                            | 82 |

|   |                | 4.3.1   | ISL AST Generation                                    | 82 |

|   |                | 4.3.2   | Distributed Backend                                   | 82 |

|   |                | 4.3.3   | GPU Backend                                           | 84 |

| 5 | Exp            | oerime  | nts                                                   | 89 |

| 6 | Dis            | cussion | 1                                                     | 97 |

| 7 | 7 Related Work |         | 103                                                   |    |

| 8 | 8 Conclusion   |         | 105                                                   |    |

# List of Figures

| 1-1  | 2D blur example showing three consecutive applications of the stencil, |    |

|------|------------------------------------------------------------------------|----|

|      | as well as the computation for the blur of the upper left pixel        | 19 |

| 1-2  | Simple single-threaded CPU-only version of a 2D blur                   | 19 |

| 1-3  | Multi-threaded and vectorized 2D blur                                  | 20 |

| 1-4  | Executing the blur on the GPU                                          | 21 |

| 1-5  | Executing the blur cooperatively on the CPUs and GPUs                  | 22 |

| 1-6  | Describing the blur algorithm with our approach                        | 23 |

| 1-7  | Vectorizing and parallelizing code with our approach                   | 23 |

| 1-8  | Generating GPU code with necessary communication with our approach.    | 23 |

| 1-9  | Additional scheduling commands needed to generate cooperative het-     |    |

|      | erogeneous code.                                                       | 23 |

| 2-1  | Shared memory multicore system                                         | 26 |

| 2-2  | NUMA (non-uniform memory access) configuration                         | 28 |

| 2-3  | UMA (uniform memory access) configuration                              | 28 |

| 2-4  | Applying vectorization to an elementwise array addition                | 32 |

| 2-5  | Simple usage of OpenMP compiler directive for parallelizing a loop     | 34 |

| 2-6  | Basic usage of the Pthreads API for parallelizing a loop               | 35 |

| 2-7  | Distributed system overview                                            | 38 |

| 2-8  | Bus-based distributed system                                           | 39 |

| 2-9  | Switch-based distributed system                                        | 39 |

| 2-10 | Simple MPI program with two ranks                                      | 42 |

| 2-11 | Two process distributed matrix-vector multiply using blocking commu-   |        |

|------|------------------------------------------------------------------------|--------|

|      | nication                                                               | 45     |

| 2-12 | Timeline showing sequential communication within a rank due to the     |        |

|      | use of blocking functions                                              | 46     |

| 2-13 | Two process distributed matrix-vector multiply combining blocking      |        |

|      | and non-blocking communication                                         | 47     |

| 2-14 | Timeline showing overlapping communication and computation with        |        |

|      | non-blocking functions                                                 | 48     |

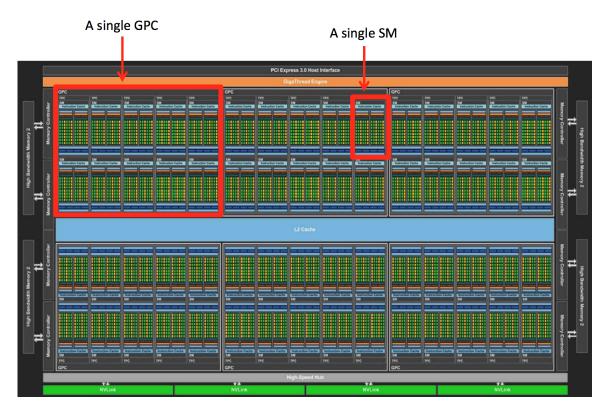

| 2-15 | Overall architecture of the NVIDIA Pascal GP100 GPU [34]               | 50     |

| 2-16 | SM configuration of the NVIDIA Pascal GP100 GPU [34]                   | 50     |

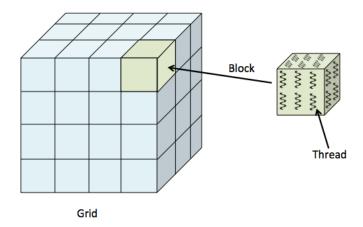

| 2-17 | Grid, block, thread hierarchy.                                         | 52     |

| 2-18 | A sequential loop and the equivalent CUDA kernel for parallel execu-   |        |

|      | tion on the GPU                                                        | 54     |

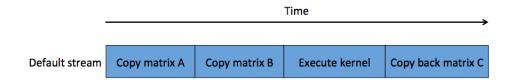

| 2-19 | CUDA code for synchronous communication and kernel execution           | 55     |

| 2-20 | Timeline for kernel execution and communication using only synchronous |        |

|      | CUDA operations                                                        | 56     |

| 2-21 | CUDA code for a combination of asynchronous and synchronous com-       |        |

|      | munication and kernel execution                                        | 57     |

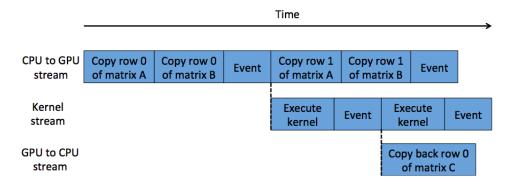

| 2-22 | Timeline for kernel execution and communication using a combination    |        |

|      | of synchronous and asynchronous CUDA operations                        | 58     |

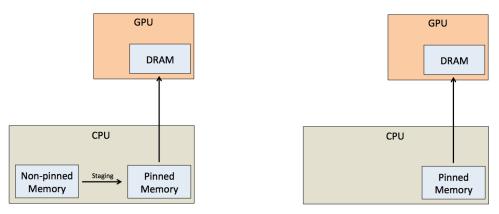

| 2-23 | Copying to GPU DRAM without pinning memory beforehand (left),          |        |

|      | and copying with pinning beforehand                                    | 59     |

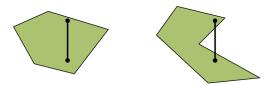

| 3-1  | Original two-level loop nest (3-1a) and three example loop nest trans- |        |

|      | formations under the polyhedral model                                  | 65     |

| 3-2  | A convex (left) vs non-convex polyhedron                               | 66     |

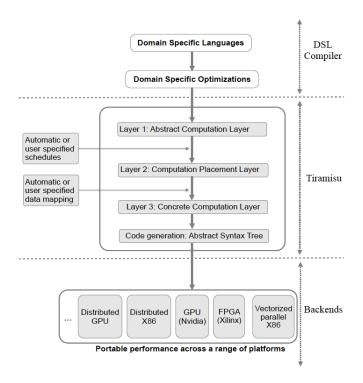

| 3-3  | TIRAMISU overview [53]                                                 | 69     |

| 4-1  | TIRAMISU code for creating a distributed loop nest with tag_distribute | _level |

|      | and the resulting pseudocode for the loop nest                         | 74     |

| 4-2 | TIRAMISU code for using separate_at and tag_distribute_level in                           |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | the resulting pseudocode for the loop nests                                               | 76 |

| 4-3 | Creating data transfers that have independent send and recv functions                     |    |

|     | with create_xfer                                                                          | 79 |

| 4-4 | Creating a single send and receive with create_xfer                                       | 80 |

| 4-5 | Converting a for loop to a conditional                                                    | 83 |

| 4-6 | Converting a loop nest to a GPU kernel                                                    | 86 |

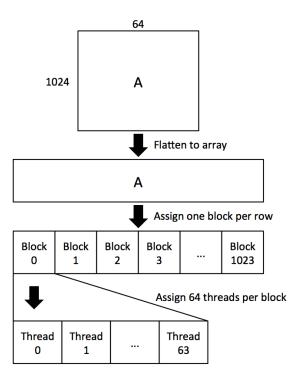

| 4-7 | Mapping matrix A as a 1D grid of 1024 1D blocks, each containing 64                       |    |

|     | threads. Matrices $B$ and $C$ would be similarly mapped. $\ \ \ldots \ \ldots \ \ \ldots$ | 87 |

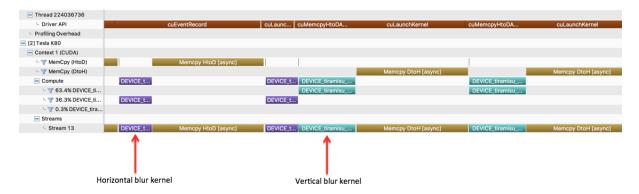

| 5-1 | Timeline for synchronous execution of the blur                                            | 91 |

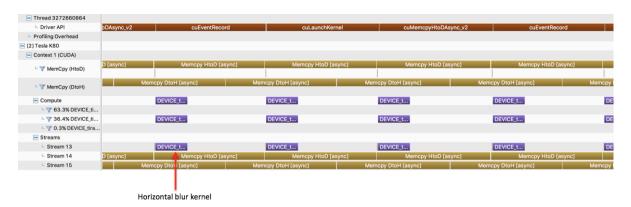

| 5-2 | Timeline for asynchronous execution of the blur                                           | 91 |

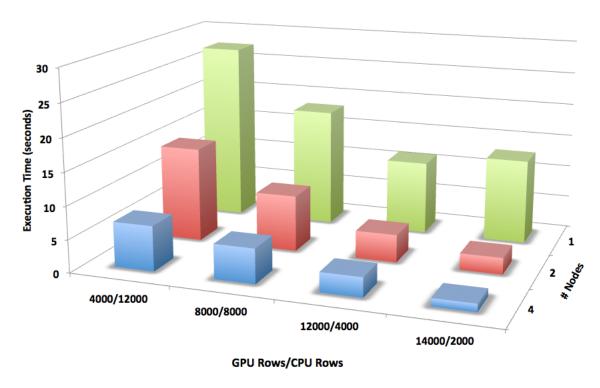

| 5-3 | 3D chart for blur with cooperative execution using asynchronous exe-                      |    |

|     | cution and communication                                                                  | 92 |

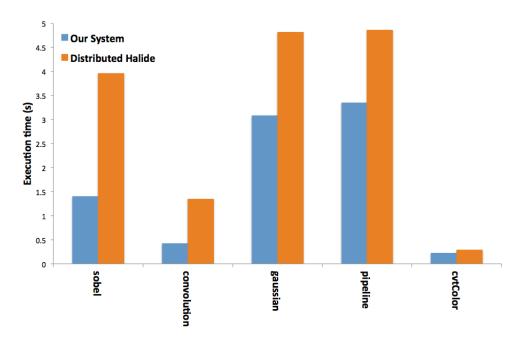

| 5-4 | Results comparing the performance of our distributed system versus                        |    |

|     | Distributed Halide on 16 CPU nodes                                                        | 95 |

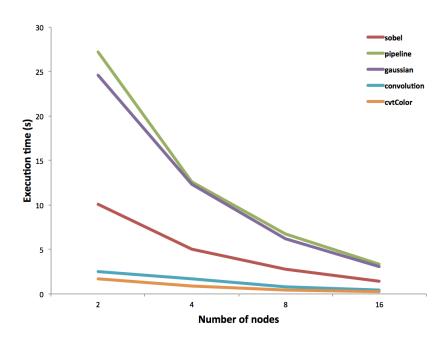

| 5-5 | The performance of our distributed system across 2, 4, 8, and 16 CPU                      |    |

|     | nodes.                                                                                    | 96 |

# List of Tables

| 2.1 | Average sizes and access latencies for a typical shared memory system |    |

|-----|-----------------------------------------------------------------------|----|

|     | [48]                                                                  | 27 |

| 2.2 | Architecture comparison between different generations of NVIDIA GPUs  |    |

|     | [34]                                                                  | 51 |

| 3.1 | Example TIRAMISU scheduling commands that transform the iteration     |    |

|     | domain in Layer I [53]                                                | 72 |

| 5.1 | Times for tiled, parallelized, and vectorized blur on a single shared |    |

|     | memory CPU node                                                       | 90 |

| 5.2 | Times for blur on GPUs using synchronous and asynchronous config-     |    |

|     | urations                                                              | 90 |

| 5.3 | Times for blur with cooperative execution using asynchronous execu-   |    |

|     | tion and communication. We use 20 CPU cores and 1 GPU per node.       | 92 |

| 5.4 | Times for blur on distributed CPUs where the ghost zones must be      |    |

|     | transferred                                                           | 93 |

| 5.5 | Times for blur where execution and memory are bound to the same       |    |

|     | sockets (matching), separate sockets (mismatch), and not bound        |    |

|     | $(\mathbf{non\text{-}NUMA})$                                          | 94 |

# Chapter 1

## Introduction

In recent years, the tech industry has seen a proliferation of different computing architectures, each touting different benefits such as performance, memory availability, programming simplicity, cost, etc. For example, in 2007, NVIDIA released their CUDA [30] software package, which made programming GPUs feasible for applications other than graphics, thus bringing their GPU architecture into the high performance computing world. GPUs offer the potential for high throughput of massively parallel applications thanks to their high number of cores. Later on in 2012, Intel released the Xeon Phi co-processor [8], followed by the Knights Landing processor [50] in 2013. These CPU chips contain many more cores than previous Intel multicore chips, providing greater throughput for operations at the cost of reduced speeds of individual cores (similar to the GPU). Combining different architectures, such as these, results in large, interconnected heterogeneous systems with distributed multisocket CPUs, GPUs, and possibly even other compute devices like FPGAs. One of the world's fastest heterogeneous supercomputers, the TSUBAME 3.0 from Japan, is equipped with over 2.160 interconnected Tesla P100 GPUs and 15.120 Intel Xeon E5-2680 v4 cores [52]. Trying to write code that utilizes even a small subset of the available compute devices on a machine such as this is a significant undertaking.

Individual instances of these architectures are hard enough to generate code for, let alone optimize them. As we will see in section 1.0.1, combining the systems only increases the difficulty of writing the code. There are numerous factors to consider

when optimizing code, as everything from the application itself to the architecture to the programming language can impact performance. It is not even guaranteed that an optimization will help; sometimes, an optimization that improves performance on its own may end up hurting performance when composed with other optimizations. Optimization is largely a trial-and-error process, and it is infeasibile to manually try a large number of different compositions of optimizations, particularly across different architectures where code portability is very limited. This often leads to code that does not reach its full performance potential.

In this thesis, we focus on abstracting multi-socket/distributed CPU and heterogeneous architectures and present programmers with a simpler interface for programming and optimizing these systems. In particular, we look at the following architectures and configurations:

Shared memory: A shared memory architecture consists of processors and memories sharing an interconnect network. The processors all share a global memory space and communicate and synchronize with each other via load and store operations to the global memory [44]. The physical memory can be separate, giving a non-uniform memory access (NUMA) system, where the load and store operations' performance varies based on the processor's location to the memory.

**Distributed memory**: A distributed memory architecture is a collection of local memories and processors connected with an interconnect network. Unlike shared memory, there is no global memory, so explicit data movement is needed between the individual local memories [44].

Heterogeneous: A heterogeneous architecture contains different types of processors with different execution models, such as a combination of CPUs and GPUs. This is opposed to a homogeneous system that contains only one type of processor, such as just CPUs [60]. In a heterogeneous programming model, computations run on one type of processor at a time. For example, in a CPU-GPU heterogeneous model, a computation can run in parallel across multiple

CPUs or multiple GPUs, but it would not execute on both the CPUs and GPUs simultaneously.

Cooperative: Cooperative computing is a programming model for a heterogeneous system. In this model, a given part of an application is partitioned to execute on the various processor types simultaneously, thus maximizing the set of computing resources utilized [56]. This is opposed to the heterogeneous model described above, where part of the application runs on either the CPU or GPU, but not both.

Beyond actual code optimizations, these large interconnected systems present other difficulties such as load balancing and communication, to name a few. Unbalanced workloads lead to poor performance since not all the resources are being utilized; communication is required for individual nodes to synchronize with each other, but is very costly, so it needs to be carefully implemented. Achieving the full compute potential of these large heterogeneous systems should be a priority, especially in cooperative configurations; as problem sizes increase, we will need as much compute power as possible. We cannot rely much longer on Moore's Law to provide us with faster processors, so improving performance is going to rely heavily on the power of cooperative execution on distributed and heterogeneous systems. We utilize the idea of separating the algorithm from the actual implementation in our work, abstracting the underlying hardware and looking at optimizations as transformations on top of the algorithm. Taking advantage of prior work on TIRAMISU, a mid-level compiler for shared memory optimizations, we implement primitives and functions that expose distributed, heterogeneous, and cooperative code generation and optimization to the programmer through a high-level scheduling language. These optimizations describe transformations on the loop nests, so the programmer does not have to change the algorithm when trying a new optimization, they just have to select a different scheduling function. Our system can generate code for shared memory, distributed memory, and heterogeneous systems, as well as code for cooperative execution on heterogeneous systems. The type of code generated is based on the schedule applied by the programmer.

Our work makes it simpler for a programmer to explore the tradeoff space between each of these systems and optimize code appropriately. The trial-and-error process is still there—it is inherent to optimization; however, our work keeps the programmer from having to make significant changes to the structure of their code just to try out an optimization.

How to design a completely unified representation for programing and optimizing these systems is still very much an open research question. However, this thesis provides building blocks for achieving that representation. We look at similarities and differences between architectures and programming models with the goal of understanding what set of features should be exposed to the programmer. In particular, we focus on the tradeoff between computation and communication, where communication means explicitly transferring data between different memories. The cost of communication may, for example, outweigh the benefits of GPU execution, so this tradeoff space needs to be explored. This work exposes communication directly to the programmer using a set of abstractions atop the underlying communication paradigm. This allows programmers to optimize communication along side the computations and maximize the overall performance of their application code.

### 1.0.1 A Motivating Example

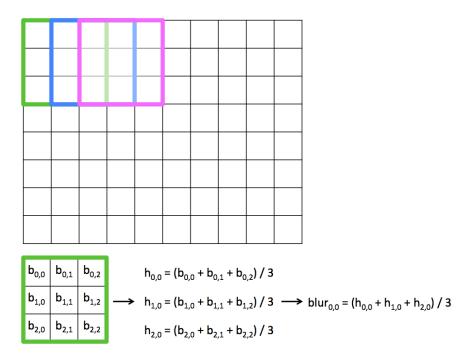

To demonstrate how much an implementation can change based on the architecture and optimizations, we provide a few handcoded examples. The application here is a 2-dimensional box blur stencil. This is a simple stencil commonly used in image processing applications. The stencil computation for the blur is shown in 1-1. It computes an average of all the pixels within the stencil and then slides one column over and does the same computation until the whole image has been processed.

The basic single-threaded code for a box blur looks like the code in figure 1-2. This code is a direct translation of the blur algorithm in figure 1-1. For high-performance code, we would not want to write the code this way, however. It would be too slow.

Figure 1-3 shows the resulting code if we apply parallelization and vectorization

Figure 1-1: 2D blur example showing three consecutive applications of the stencil, as well as the computation for the blur of the upper left pixel.

```

1 ...

void blur() {

for (unsigned long r = 0; r < rows+2; r++) {

3

4

for (unsigned long c = 0; c < cols; c++) {</pre>

temp[r*cols+c] = (input[r*cols+c] + input[r*cols+c+1] +

5

input[r*cols+c+2]) / 3.0f;

6

}

7

8

for (unsigned long r = 0; r < rows; r++) {

9

for (unsigned long c = 0; c < cols; c++) {</pre>

\operatorname{output}[r*\operatorname{cols+c}] = (\operatorname{temp}[r*\operatorname{cols+c}] + \operatorname{temp}[(r+1)*\operatorname{cols+c}] +

10

temp[(r+2)*cols+c]) / 3.0f;

}

11

12

}

13 }

14

```

Figure 1-2: Simple single-threaded CPU-only version of a 2D blur.

```

void blur_par_vec() {

omp_set_num_threads(20);

__m128 div_by = _mm_set_ps1(3.0f);

#pragma omp parallel for schedule(static, std::max((int)(rows/20), 1))

for (ulong r = 0; r < rows+2; r++) {

for (ulong c = 0; c < cols; c+=4) {

__m128 input_load_0 = _mm_loadu_ps(&input[r*cols+c]);

__m128 input_load_1 = _mm_loadu_ps(&input[r*cols+c+1]);</pre>

6

7

__m128 input_load_2 = _mm_loadd_ps(&input[r*cols+c+2]);

__m128 sum = _mm_add_ps(_mm_add_ps(input_load_0, input_load_1), input_load_2);

__m128 res = _mm_div_ps(sum, div_by);

10

11

12

mm_storeu_ps(&temp[r*cols+c], res);

#pragma omp parallel for schedule(static, std::max((int)(rows/20), 1))

15

for (ulong r = 0; r < rows; r++) {</pre>

cr (ulong r = 0; r < rows; r++) {

for (ulong c = 0; c < cols; c+=4) {

__m128 temp_load_0 = _mm_loadu_ps(&temp[r*cols+c]);

__m128 temp_load_1 = _mm_loadu_ps(&temp[(r+1)*cols+c]);

__m128 temp_load_2 = _mm_loadu_ps(&temp[(r+2)*cols+c]);

__m128 temp_load_2 = _mm_loadu_ps(&temp[(r+

17

18

19

20

__m128 temp_load_2 = _mm_loadu_ps(&temp[(r+1)*cols+c]);

__m128 sum = _mm_add_ps(_mm_add_ps(temp_load_0, temp_load_1), temp_load_2);

__m128 res = _mm_div_ps(sum, div_bv):

22

23

_mm_storeu_ps(&output[r*cols+c], res);

```

Figure 1-3: Multi-threaded and vectorized 2D blur.

(discussed in section 2.1.2). These are two common shared memory optimizations. In this code, the algorithm is still the same—we use two loop nests to compute the two parts of the blur, but the implementation has changed. There are more levels in the loop nests and the loop bodies now use vector instructions.

Next, we implement the blur to execute on the GPU. Figure 1-4<sup>1</sup> shows code for running the blur on a single GPU. It is still the same algorithm, but the implementation has completely changed from the previous versions. The two loop nests become the two GPU functions shown at the top, and then calling those functions adds additional code. If we switch to a cooperative setting, the code becomes even more complicated. Figure 1-5 shows code that runs cooperatively on the CPU and GPU for the blur. We need multiple versions of the code depending on the architecture, and if any change is made to the algorithm, such as adding a third dimension to the blur, each version of the code would need to be changed independently, unnecessarily adding additional burden the programmer.

Using our scheduling language approach described throughout this thesis, we can generate the same code with much less effort. Figure 1-6 shows our syntax for creating the initial blur algorithm. We then apply scheduling to that algorithm to describe the optimizations and guide the code generation. Figure 1-7 shows the schedule

<sup>&</sup>lt;sup>1</sup>Error checking and some linking functions for the CUDA code excluded for brevity.

```

__global__

void blur_cuda_async_kernel_bx(float *input, float *bx, ulong *_cols, ulong *

_current_row) {

ulong cols = *_cols;

ulong current_row = *_current_row;

int block_size = 32;

bx[current_row*cols+blockIdx.x*block_size+threadIdx.x] = (input[current_row*(cols

+2)+blockIdx.x*block_size+threadIdx.x] + input[current_row*(cols+2)+blockIdx.x*

block_size+threadIdx.x+1] + input[current_row*(cols+2)+blockIdx.x*block_size+

threadIdx.x+21) / 3.0f:

7

}

_global__

void blur_cuda_async_kernel_by(float *bx, float *by, ulong *_cols, ulong *

_current_row) {

10

ulong cols = *_cols;

11

ulong current_row = *_current_row;

12

int block_size = 32;

13

by[current_row*cols+blockIdx.x*block_size+threadIdx.x] = (bx[current_row*cols+

blockIdx.x*block_size+threadIdx.x] + bx[current_row*cols+blockIdx.x*block_size+

threadIdx.x+cols] + bx[current_row*cols+blockIdx.x*block_size+threadIdx.x+2*

cols]) / 3.0f;

15

void blur_gpu() {

16

CUdeviceptr d_input, d_by, d_bx;

cuMemAlloc(&d_input, (this->rows+2) * (this->cols+2) * sizeof(float));

17

18

cuMemAlloc(&d_bx, this->rows * this->cols * sizeof(float));

cuMemAlloc(&d_by, this->rows * this->cols * sizeof(float));

19

20

CUdeviceptr d_kernel_vals_0, d_kernel_vals_1; cuMemAlloc(&d_kernel_vals_0, this->rows * sizeof(ulong)); cuMemAlloc(&d_kernel_vals_1, this->rows * sizeof(ulong));

21

22

23

24

CUstream h2d_stream, d2h_stream, kernel_stream;

cuStreamCreate(&h2d_stream, CU_STREAM_DEFAULT);

cuStreamCreate(&d2h_stream, CU_STREAM_DEFAULT);

25

26

27

cuStreamCreate(&kernel_stream, CU_STREAM_DEFAULT);

for (ulong r = 0; r < this->rows; r++) {

cuMemcpyHtoDAsync(d_input + r * (this->cols+2) * sizeof(float), &input[r * (this

28

29

->cols+2)], this->cols * sizeof(float), h2d_stream);

cuMemcpyHtoDAsync(d_kernel_vals_0+r*sizeof(ulong), &cols, sizeof(ulong),

30

kernel_stream);

31

cuMemcpyHtoDAsync(d_kernel_vals_1+r*sizeof(ulong), &r, sizeof(ulong),

kernel_stream);

CUevent h2d_event;

cuEventCreate(&h2d_event, 0);

cuEventRecord(h2d_event, h2d_stream);

33

34

CuStreamWaitEvent(kernel_stream, h2d_event, 0);

CUdeviceptr k0 = d_kernel_vals_0+r*sizeof(ulong);

CUdeviceptr k1 = d_kernel_vals_1+r*sizeof(ulong);

void *kernel_args_bx[] = {&d_input, &d_bx, &k0, &k1};

cuLaunchKernel(bx_kernel, this->cols / 5, 1, 1, 5, 1, 1, 0, kernel_stream,

35

36

37

38

39

kernel_args_bx, 0);

40

for (ulong r = 0; r < this->rows; r++) {

41

cuMemcpyHtoDAsync(d_kernel_vals_0+r*sizeof(ulong), &cols, sizeof(ulong),

42

kernel_stream);

43

cuMemcpyHtoDAsync(d_kernel_vals_1+r*sizeof(ulong), &r, sizeof(ulong),

kernel_stream);

CUdeviceptr k0 = d_kernel_vals_0+r*sizeof(ulong);

CUdeviceptr k1 = d_kernel_vals_1+r*sizeof(ulong);

void *kernel_args_by[] = {&d_bx, &d_by, &k0, &k1};

cuLaunchKernel(by_kernel, this->cols / 5, 1, 1, 5, 1, 1, 0, kernel_stream,

44

45

46

47

kernel_args_by, 0);

48

CUevent kernel_event;

cuEventCreate(&kernel_event, 0);

cuEventRecord(kernel_event, kernel_stream);

49

50

cuStreamWaitEvent(d2h_stream, kernel_event, 0);

CUdeviceptr kd_by = d_by + r * (this->cols) * sizeof(float);

cuMemcpyDtoHAsync(&by[r * this->cols], kd_by, this->cols * sizeof(float),

51

52

53

d2h_stream);

55

cuCtxSynchronize();

```

Figure 1-4: Executing the blur on the GPU.

```

__global__

void blur_cuda_async_kernel_bx(float *input, float *bx, ulong *_cols, ulong *_current_row) {

ulong cols = *_cols;

ulong current_row = *_current_row;

int block_size = 32;

bx[current_row*cols*blockIdx.x*block_size*threadIdx.x] = (input[current_row*(cols*2)*blockIdx.x*block_size*threadIdx.x] + input[current_row*(cols*2)*blockIdx.x*block_size*threadIdx.x*] + input[current_row*(cols*2)*blockIdx.x*block_size*threadIdx.x*] / 3.0f;

}

\frac{3}{4} \frac{4}{5} \frac{6}{6}

8

9

10

}

void blur_cooperative {

void blur_cooperative {

...

int provided = -1;

MPI_Init_thread(NULL, NULL, MPI_THREAD_FUNNELED, &provided);

int rank;

MPI_Comm_rank(MPI_COMM_WORLD, &rank);

int total_procs = NUM_CPU_PROCS + NUM_GPU_PROCS;

if (rank <= NUM_CPU_PROCS) {

omp_set_num_threads(20);

__m128 div_by = _mm_set_ps1(3.0f);

#pragma omp parallel for schedule(static, std::max((int)((rows/total_procs)/20), 1))

for (ulong r = 0; r < (rows/total_procs)+2; r++) {

for (ulong c = 0; c < cols; c+4) {

__m128 input_load_0 = _mm_loadu_ps(&input[r * cols + c]);

__m128 input_load_1 = _mm_loadu_ps(&input[r * cols + c + 1]);

__m128 input_load_2 = _mm_loadu_ps(&input[r * cols + c + 2]);

__m128 sum = _mm_add_ps(_mm_add_ps(_input_load_0, input_load_1), input_load_2);

__m128 sum = _mm_div_ps(sum, div_by);

__mm_storeu_ps(&temp[r * cols + c], res);

}

</pre>

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

ma omp parallel for schedule(static, std::max((int)((rows/total_procs)/20), 1))

or (ulong r = 0; r < (rows/total_procs); r++) {

for (ulong c = 0; c < cols; c+=4) {

__m128 temp_load_0 = _mm_loadu_ps(&temp[r * cols + c]);

__m128 temp_load_1 = _mm_loadu_ps(&temp[(r + 1) * cols + c]);

__m128 temp_load_2 = _mm_loadu_ps(&temp[(r + 2) * cols + c]);

__m128 temp_load_2 = _mm_loadu_ps(&temp[(r + 2) * cols + c]);

__m128 temp_load_2 = _mm_load_ps(temp_load_0, temp_load_1), temp_load_2);

__m128 res = _mm_div_ps(sum, div_by);

_mm_storeu_ps(&output[r * cols + c], res);

}</pre>

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

61

Culdenteneries (bf_kerner, this->cols) / 5, 1, 1, 5, 1, 1, 0, kerner_stream, kerner_algs_bx, 0),

for (ulong r = 0; r < this->rows; r++) {

culwemcpyHtoDAsync(d_kernel_vals_0+r*sizeof(ulong), &cols, sizeof(ulong), kernel_stream);

culdencpyHtoDAsync(d_kernel_vals_1+r*sizeof(ulong), &r, sizeof(ulong), kernel_stream);

CUdeviceptr k0 = d_kernel_vals_0+r*sizeof(ulong);

Cudeviceptr k1 = d_kernel_vals_1+r*sizeof(ulong);

void *kernel_args_by[] = {&d_bx, &d_by, &k0, &k1};

culaunchKernel(by_kernel, this->cols) / 5, 1, 1, 5, 1, 1, 0, kernel_stream, kernel_args_by, 0);

CUevent kernel_event;

cuEventCreate(&kernel_event, 0);

cuEventCreate(&kernel_event, kernel_stream);

cuStreamWaitEvent(d2h_stream, kernel_event, 0);

CUdeviceptr kd_by = d_by + r * (this->cols) * sizeof(float);

culemcpyDtoHAsync(&by[r * this->cols], kd_by, this->cols * sizeof(float), d2h_stream);

}

cuMemFree(d_input);

cuMemFree(d bv);

MPI Barrier(MPI COMM WORLD):

MPI_Finalize();

```

Figure 1-5: Executing the blur cooperatively on the CPUs and GPUs.

for generating parallelized and vectorized code. In figure 1-8, we see the code for generating GPU code. Finally, we have the cooperative code. These schedules largely remain the same; we only need a few additional scheduling commands, shown in figure 1-9. With these minor modifications, we get OpenMP+CUDA+MPI code with much less code than the hand-written counterpart.

Figure 1-6: Describing the blur algorithm with our approach.

```

1  var r0("r0"), r1("r1"), c0("c0"), c1("c1");

2  bx.split(r, rows/20, r0, r1); by.split(r, rows/20, r0, r1);

3  by.tag_parallel_level(r0); bx.tag_parallel_level(r0);

4  bx.split(c, 8, c0, c1); by.split(c, 8, c0, c1);

5  by.tag_vector_level(c1, 8); bx.tag_vector_level(c1, 8);

6  bx.before(by, root);

```

Figure 1-7: Vectorizing and parallelizing code with our approach.

```

xfer_prop h2d_cuda_async(p_float32, {ASYNC, CUDA, CPU2GPU}, 1);

xfer_prop d2h_cuda_async(p_float32, {ASYNC, CUDA, GPU2CPU}, 2);

xfer_prop d2h_cuda_async_kernel_stream(p_float32, {ASYNC, CUDA, GPU2CPU}, 0);

xfer_prop h2d_cuda_async_kernel_stream(p_float32, {ASYNC, CUDA, CPU2GPU}, 0);

xfer h2d = computation::create_xfer("{h2d[r,c]: 0<=r<" + srows + " and 0<=c<2.

+ scols + "}", h2d cuda asvnc.

and 0 \le c \le 2 +

blur_input(r,c), &blur);

tiramisu::wait h2d_wait("{h2d_wait[r,c]: 0<=r<" + srows + " and 0<=c<1}", h2d.os(r,0),

h2d_cuda_async_kernel_stream, true, &blur);

tiramisu::wait d2h_wait_for_by("{d2h_wait_for_by[r,c]: 0<=r<" + srows + " and 0<=c<1}", by(r, 0), d2h_cuda_async,

8

true, &blur);

tiramisu:: wait \ d2h\_wait("\{d2h\_wait[r,c]: \ 0 < = r < " + srows + " \ and \ 0 < = c < 1\}", \ d2h.os(r,0), \ h2d\_cuda\_async, \ true, \ \& true, \ d2h.os(r,0), \ h2d\_cuda\_async, \ \ h2d\_cu

blur);

generator::update_producer_expr_name(bx, "blur_input", "h2d", false);

h2d.os->collapse_many({collapser(1, 0, COLS+2)});

d2h.os->collapse_many({collapser(1, 0, COLS)});

bx.split(c, BLOCK_SIZE, c0, c1); by.split(c, BLOCK_SIZE, c0, c1);

d2h_wait.before(*h2d.os, r);

h2d.os->before(h2d_wait, r);

h2d_wait.before(bx, r);

bx.before(by, root);

by.before(d2h_wait_for_by, r);

d2h_wait_for_by.before(*d2h.os, r);

bx.tag_gpu_level2(c0, c1, 0); by.tag_gpu_level2(c0, c1, 0);

```

Figure 1-8: Generating GPU code with necessary communication with our approach.

```

// Apply to the CPU and GPU

bx.split(r, rows/PROCS, q1, q2); by.split(r, rows/PROCS, q1, q2);

bx.tag_distribute_level(q1); by.tag_distribute_level(q1);

// Apply to the GPU only

blur.rank_offset = -1*PROCS;

```

Figure 1-9: Additional scheduling commands needed to generate cooperative heterogeneous code.

# Chapter 2

# System Architecture Background

### 2.1 Shared Memory Systems

A shared memory system is made up of multiple processors and memories that are connected by an interconnect network. The individual processors in the network communicate with each other implicitly via load and store operations between the processor's memories. These systems, while easier to prgram than their distributed and heterogeneous counterparts, have a myriad of optimization opportunities available, and optimizing shared memory code is still an active area of research.

#### 2.1.1 Architecture and Execution Overview

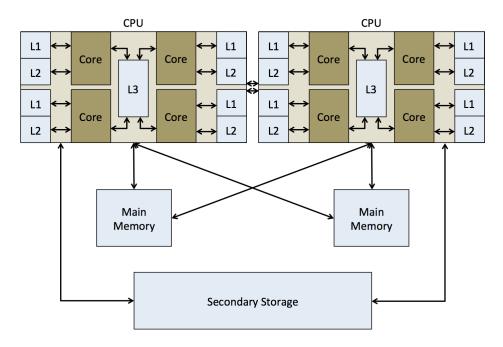

In a shared memory system, all the processors share the same address space, meaning all the processors have access to the same memory. Any processor can access the main memory, as well as the memory in the private caches of other processors, using *load* and *store* operations. The underlying hardware handles all communication implicitly between the different memories and the cores, which is in contrast to *distributed memory systems* discussed in section 2.2. However, programmer intervention is needed to achieve high-performance, as the hardware can only optimize so much. An example configuration of a shared memory multicore system is depicted in figure 2-1. This figure is based off of the Intel Skylake architecture [49].

Figure 2-1: Shared memory multicore system.

This architecture shows a dual-socket configuration with four cores per socket (each socket takes one CPU, and each CPU contains four cores). Each socket has the same configuration. Within a socket, each core has its own L1 cache (both instruction and data), as well as its own L2 cache. The L3 cache, also known as the last-level cache, is shared by each of the cores in a socket. The caches and cores on an individual socket communicate across a bus. The two sockets are connected by some other high-speed interconnect. For example, in the case of the Intel Skylake architecture, up to 8 different sockets can be connected with Intel Ultra Path Interconnect (UPI) [27]. UPI is a low-latency, power-efficient interconnect for connecting Intel CPUs. Each socket connects to the main memory and secondary memories through another interconnect.

Memory is configured as a hierarchy, and each level presents a tradeoff between memory size and access *latency*. Latency is the time required to complete an event, such as a memory access [19]. Table 2.1 shows a typical memory hierarchy for a personal shared memory system, along with the average memory sizes and access latencies. At the top of this hierarchy, there are the registers, which have the lowest latency. As you move down the hierarchy, the latency increases, with secondary memory having the highest latency. However, the size of the memory increases as

| Memory     | Avg. Size | Avg. Access Latency |

|------------|-----------|---------------------|

| Registers  | 1000B     | 300 ps              |

| L1         | 64KB      | 1ns                 |

| L2         | 256KB     | 10ns                |

| L3         | 4MB       | $20 \mathrm{ns}$    |

| RAM        | 16GB      | 100ns               |

| Hard Drive | 16TB      | $10 \mathrm{ms}$    |

Table 2.1: Average sizes and access latencies for a typical shared memory system [48].

you move down the hierarchy. Ideally, all the necessary data for a process would be located in caches, but that is not always possible, particularly for programs with large working set sizes.

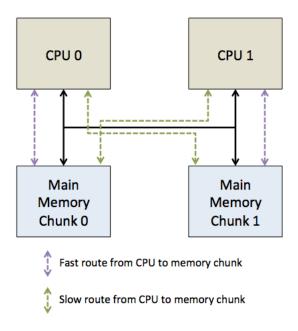

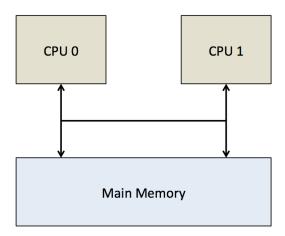

In figure 2-1, notice that the main memory is separated into two individual chunks. Even though a shared memory system has a single address space, the underlying physical memory may be separate across the CPUs. This is type of configuration is referred to non-uniform memory access (NUMA), or distributed shared memory. A simpler view of a NUMA system is in figure 2-2. In this setup, cores can access addresses in their part of the distributed memory faster than the other parts, so they have non-uniform access latency. This is in contrast to a uniform memory access (UMA) configuration where the physical memory is in one centralized location. With an UMA system, all cores have the same memory access latency for a given address, hence the uniform access. UMA can be used with single socket systems that have a small number of cores. As the number of cores increase, there is too much contention on the centralized memory, severely impacting performance [19]. A simple UMA configuration is depicted in figure 2-3.

#### Accessing Data in a Shared Memory System

When a load or a store is issued by a core in a shared memory system, the hardware performs several steps to access the data and get it to the requesting core. Though this is handled automatically by the hardware, a programmer can influence the performance of these steps based on how they write their program. The first step the hardware takes is locating the data, which begins by checking the core's caches. If the

Figure 2-2: NUMA (non-uniform memory access) configuration.

Figure 2-3: UMA (uniform memory access) configuration.

data is not found in the cache, the hardware will check the caches of the other cores. If the address is not found in any of the caches, then the main memory is checked. If the address is not found in main memory, then secondary memory is checked, and so on. Each access is progressively more expensive, so the further into the memory hierarchy the hardware searches, the higher the access latency.

Once the data is located, it needs to be moved to the appropriate location for the requesting core. For loads, this typically means moving the data to the requesting core's L1 cache. For stores, the data may be first moved to the L1 cache (if it is a write-back cache), or it may be left in the current location (for a write-through cache) [44]. If the data is already in the L1 cache, then there is nothing to be done (this is the ideal case). If the data is located somewhere else, then it is moved into the L1 cache, and possibly also the L2 and L3 cache, depending on their configuration.

Data is not moved as a single byte. When data is moved from secondary memory, the data is moved in whole *pages*, where a page is a chunk of data typically around 4KB in size, though there are large pages as well. This means accessing a single address in secondary memory will cause an entire page worth of data to be moved into main memory. Accessing a page involves converting a *virtual address* to a *physical address*, which is done with a *page table lookup*. This translation introduces extra overhead, increasing the latency of accessing secondary memory.

A cache operates similarly, but data is moved from from main memory as a *cache line* instead, which is usually either 32B or 64B. When the data is finally read from cache, it is moved as a word, which is 4B or 8B.

In a shared memory system, it is possible for the same piece of data to be located in multiple memory locations, such as the L1 caches of different cores. When a core issues a store, any caches containing that address need to be signaled that their data is now stale. If the data was kept in cache without being marked as stale, cores would end up using old copies of the data, possibly resulting in incorrect computations. More precisely, any reads done by another core to that same address need to return the most recent value for that address. This is known as *cache coherence* [46]. The hardware is responsible for maintaining coherency.

The hardware is also responsible for maintaining *cache consistency*. Cache consistency deals with the relative order that cores see stores completed to different addresses (i.e. when does a read see written data) [47]. A programming language should abstract the memory consistency model and provide primitives such as locks, semaphores, and atomics to the programmer.

### 2.1.2 High Performance Shared Memory Code

The average programmer has more than likely written code for shared memory systems. While the hardware automatically handles much of the data transfer and synchronization in a shared memory system, there are numerous optimizations that can be made on a software level to improve on what the hardware does, so a high performance programming language needs to support these optimizations. We will look at some examples of loop transformations here, namely caching, vectorization, and parallelization, as well as NUMA-awareness, and discuss their performance benefits. These optimizations are integral parts of the TIRAMISU framework that this thesis utilizes.

#### Caching

Caching can have a tremendous impact on the performance of shared memory code. Ineffective or naive use of the cache can cause unnecessary latency due to events such as eviction, ping-ponging, and/or false sharing. Eviction is when a particular piece of data is removed from cache. If data is evicted, but still needed, it will have to be brought back into cache. If the cache constantly evicts a piece of data, and then brings it back in over and over again, this is ping-ponging. False sharing occurs when different cores access data that shares a cache line. If the cores keep writing to those different addresses, even though they are separate, the whole cache line will keep getting bounced back and forth between their two caches since the whole line keeps getting evicted. This can pose a severe bottleneck.

Related to caching is data locality. There are two types of data locality, spatial

and temporal. Spatial locality refers to multiple addresses. It means that if a memory address is accessed, other memory addresses near it are likely to be accessed in the near future. Since a cache brings in data as a whole cache line, we want our code to access the data in that cache line before it gets evicted from the cache, if possible. Temporal locality refers to a single address. If an address is accessed, temporal locality says that same address will be accessed again in the near future. This means we want to keep the data in cache—if we evict it too soon, we will just have to bring the cache line back in, which takes additional time.

One of the loop transformations used to improve locality is loop tiling. Loop tiling splits and reorganizes a loop nest so that the outer loops iterate over blocks of tiles. Within the tiles, the individual data points are iterated over. Note that tiles do not have to be rectangular, they can theoretically be any shape, but some tile shapes work better than others depending on the loop nest.

#### Vectorization

Vectorization is a hardware feature that provides data-level parallelism though vector instructions in the ISA. It is a SIMD (single instruction, multiple data) operation where the same instruction is applied to different pieces of data in parallel. Current vector instructions sets in x86 ISA today include AVX-512 [42] and SSE4 [28].

Vector instructions execute on special vector hardware, which are similar to ALUs, but operate on vector registers. These registers are larger than general purpose registers, with current vector registers being up to 512 bytes in size. Multiple pieces of data of the same type can be placed into a single vector register. For example, with a 256 byte vector register, you can fit 4 64-bit doubles, 8 32-bit floats, and so on. The vector units execute a vector instruction on all the data in the vector register in parallel. So, with 4 64-bit floats, you theoretically get 4x speedup for that instruction as compared to a SISD (single instruction, single data) instruction.

The code in figure 2-4a shows some simple C code for doing an elementwise addition between two arrays with 8 elements each. Figure 2-4b shows the equivalent vectorized code. The \_\_mm256 values are vector float types, so they represent 8 float

```

1 float a[8], b[8], c[8];

2 ...

3 for (int i=0; i<8; i++) {

4   c[i] = a[i] + b[i];

5 }</pre>

```

(a) An unvectorized elementwise add of two 8-element float arrays.

```

1 float a[8], b[8], c[8];

2 ...

3 __m256 vector_a = _m256_load_ps(a);

4 __m256 vector_b = _m256_load_ps(b);

5 __m256 vector_c = _m256_add_ps(vector_a, vector_b);

6 _m256_store_ps(c, vector_c);

```

(b) The vectorized version using AVX intrinsics.

Figure 2-4: Applying vectorization to an elementwise array addition.

values packed together. \_mm256\_load\_ps, \_mm\_add\_ps, and \_mm\_store\_ps are called vector intrinsics. While a compiler typically applies auto-vectorization to code, these intrinsics allow programmers to manually vectorize code.

#### Parallelization

Shared memory parallelization, also known as *symmetric multiprocessing* (SMP) is an optimization where operations in a program are partitioned and run concurrently on the cores. There are two primary types of parallelism: *data parallelism* and *task parallelism*

- 1. Data parallelism: The data is partitioned across the cores and each core executes concurrently. Usually, each core is running the same set of operations, just on a different chunk of data. *Loop parallelism* is an example of this.

- 2. Task parallelism: The operations of a program are grouped together into tasks, which are run concurrently across the cores. This typically entails running different operations on the same chunk of data.

These two types of parallelism can be combined together, which is useful as many programs benefit from both types of parallelism [38].

Parallelism applied naively to a program does not always lead to better results though, as not all programs necessarily benefit from parallel execution. *Amdahl's Law* provides an upper limit to the speedup for a program if sequential parts are parallelized (assuming the problem size is fixed). Amdahl's Law is as follows:

$$S = \frac{1}{(1-p) + \frac{p}{n}}$$

where S is the possible speedup, p is the portion of the overall program that can be parallelized, and n is the number of processors to parallelize across. While Amdahl's Law does not take into account factors such as processor type, memory issues, etc, it is great starting point when trying to decide if a program will benefit from parallelization.

Other factors such as granularity and load balancing can also impact performance. Granularity measures the ratio of the amount of computation done in a parallel region to how often a parallel operation is spawned. Fine-grained parallelization means there is a small amount of computation done by each parallel thread, while coarse-grained parallelization has a large amount of computation per thread. The correct type of parallelism to apply depends on the application. For example, a loop nest with dependencies between each iteration may not be able to be parallelized at the loop level (coarse-grained), but it may be possible to parallelize operations within the loop body itself (fine-grained).

Load balancing is an important factor in applications where threads are assigned different amounts of work. If the work is unbalanced across threads, then some might finish before others, leaving them idle while waiting for the others to complete. This results in decreased performance as not all threads are being used to their full potential.

While hardware can provide some degree of parallelism, the majority of it is defined through software. Many programming languages have APIs and libraries that can be used for parallelization. Some popular libraries for parallelizing code include OpenMP

```

1 #pragma omp parallel for

2 for (i=0; i<I; i++) {

3   for (j=0; j<J; j++) {

4     A[i*J+j] = A[i*J+j] + 4;

5   }

6 }</pre>

```

Figure 2-5: Simple usage of OpenMP compiler directive for parallelizing a loop.

[9], Pthreads [29], Thread Building Blocks [43], Cilk Plus [6], to name a few. We look at OpenMP and Pthreads in more detail as they provide a good look at the differences in these libraries.

**OpenMP** OpenMP provides an API and set of compiler directives for parallelizing a program. It is implemented in C, C++, and Fortran and can be used for both data and task parallelism. With OpenMP, a programmer simply declares that some code, such as a loop nest, should be executed in parallel. These parallel regions are specified using compiler directives. In C/C++, these are preprocessor instructions specified by the **pragma** keyword. A simple loop parallelization with OpenMP example is shown in figure 2-5. By placing the directive at the top level of the loop nest (line 1), the compiler knows that the outer loop should be parallelized [38]. The **parallel for** directive is a simple parallel directive in OpenMP, but OpenMP offers numerous other directives to fine tune parallelism.

In OpenMP, a programmer specifies what needs to be parallelized, but not how the code is parallelized. The job of determining how to parallelize the code, such as managing the threads, is left to the compiler and the runtime system.

Pthreads Pthreads, which stands for POSIX threads, is another standard for SMP in C/C++ that provides an API for creating and managing threads in a program. The standard, maintained by the IEEE, provides an API for creating and managing threads in a program. Pthreads operates at a lower level than OpenMP, so programmers are responsible for picking out the regions to parallelize and how to parallelize them. The API provides functions for thread management, mutexes, condition variables, and synchronization [29]. This offers more direct control to the programmer,

```

1 void *loop_body(void *_t_idx) {

int t_idx = (int)_t_idx;

2

3

A[t_idx] = A[t_idx] + 4;

4

pthread_exit((void*)_t_idx);

5

return NULL;

6 }

7

. . .

8 pthread_t threads[I*J];

9 int *t_idxs[I*J];

10 for (t_idx=0; t_idx<I*J; t_idx++) {

t_idxs[t_idx] = (int*)malloc(sizeof(int));

11

12

*t_idxs[t_idx] = t_idx;

13

pthread_create(&threads[t_idx], NULL, &loop_body, (void*)

t_idxs[t_idx]);

14 }

15 void *status;

16 for (t_idx=0; t_idx<I*J; t_idx++) {

// wait for threads to complete

18

pthread_join(threads[t_idx], &status);

19 }

20 pthread_exit(NULL);

21 ...

```

Figure 2-6: Basic usage of the Pthreads API for parallelizing a loop.

but requires more coding than other frameworks like OpenMP.

Figure 2-6 shows the loop nest in figure 2-5 parallelized with Pthreads instead of OpenMP. First, the loop nest body needs to be converted into a function. This is the function on lines 1 through 6. Then, we need a fair amount of code to manage the threads. Here, we create one thread for every element in A (lines 8 through 14). When the actual threads are created on line 13 with the pthread\_create function, the thread begins execution (or waits until resources are available). A *join* operation is needed to check when the thread has actually completed. This is done on lines 16 through 19 using the pthread\_join function.

#### **NUMA-Awareness**

If a system is set up in NUMA configuration, ignoring the placement of data relative to the processors can result in subpar performance. NUMA-awareness refers to code that optimizes performance based on the NUMA setup. In particular, the code must deal with data placement and processor affinity. Data placement in NUMA refers to where in physical memory data resides. For good NUMA performance, data should be placed in the physical memory local to the core using it, as the access time to local memory is faster compared to remote memory. Processor affinity is used to assign a thread or process to a specific core. Usually, the task of assigning threads to cores is left to a scheduler, but most systems have an API that can be used to direct the scheduler [37].

Both data placement and processor affinity need to be dealt with to get good NUMA performance. If a thread is assigned to a core on socket 0, but the data that core needs is placed in socket 1, then it is likely that the core will experience additional latency when accessing that data. Whenever possible, the data should be placed in the memory that is local to the core using it. One tool used to direct processor affinity and data placement is the numactl [31] command on Linux. On NUMA-capable machines, a programmer can launch their application using this command and say which cores to execute on, as well as how to bind data to memory.

### 2.1.3 Limitations of Shared Memory Systems

For many datasets and computations, shared memory systems provide enough resources. However, as the size of datasets increase, shared memory systems begin to perform poorly. Datasets may be too big to fit into the system's main memory, or even into secondary memory. When data cannot fit into main memory, swapping in from secondary memory is expensive and negatively impacts the performance of systems. Distributed memory becomes necessary in these situations. Additionally, only so many cores can be put into a shared memory system. As the number of cores increase, the amount of contention on the system bus and other interconnects from events like data access, coherence, etc. increases to a point where the system becomes unusable. Scaling up to more computing power requires distributing the computation, and/or using other resources such as GPUs. Beyond performance issues, optimized shared memory code is trickier to debug, particularly if it is parallelized, as bugs such as race conditions are easy to introduce and can cause errors or give incorrect results.

# 2.2 Distributed Memory Systems

A distributed memory system is a system made up of independent local memories and processors connected with an interconnect network. Opposed to shared memory systems, there is no single global memory, so explicit communication is required to transfer data between the local memories [57, 22]. These systems are known multiple-instruction, multiple data (MIMD) systems. The individual processors (which we refer to as nodes) could be anything from single CPUs, to full shared memory systems (called hybrid distributed memory systems [57]). Typically, it is up to the programmer to implement a communication scheme for a program. Other compute devices, such as GPUs can also be part of the system, giving a heterogeneous distributed system. Distributed memory systems scale better than shared memory systems thanks to more compute resources and more memory. However, factors such as communication, data locality, available parallelism in a program, etc, all need to be considered when writing a distributed memory program.

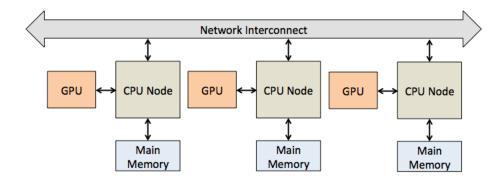

### 2.2.1 Architecture and Execution Overview

Figure 2-7 shows an example of distributed memory system made up of four shared memory nodes, with each shared memory node having an associated GPU. One of the most important components of distributed memory systems is the communication interconnect between each of the systems. In the literature, this interconnect may be referred to as *network fabric*. Many distributed systems will require some form of communication or data transfer between the individual systems (for example, if all the data starts on one of the nodes, that node will need to transfer the data to other nodes). If the communication link has high latency or low bandwidth, communication will quickly become the bottleneck, particularly in memory-bound programs.

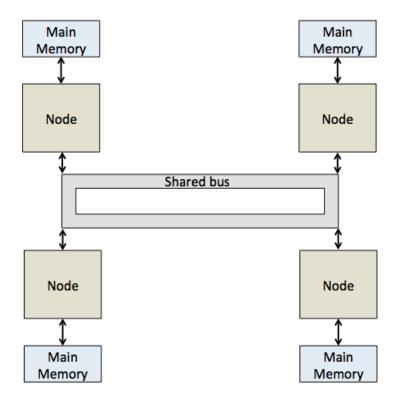

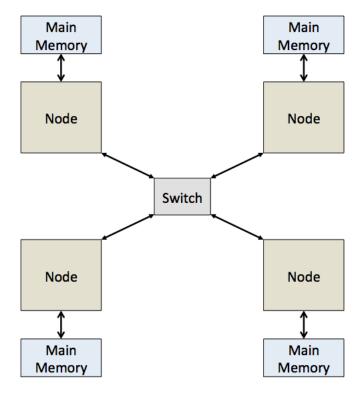

There are two primary networks used to connect a distributed memory system: bus-based and switch-based. In a bus-based network, all the nodes share the same communication interconnect (bus). If there are a lot of nodes, the bus will get very congested because every piece of data from every node travels on the same bus, re-

Figure 2-7: Distributed system overview.

gardless of its destination. In a switch-based system, nodes communicate through switches, which sends data to the destination node. This significantly reduces congestion since data only goes through interconnects leading to the destination. It is also much more scalable since new nodes just mean adding a new switch [22]. Figure 2-8 shows a bus-based network configuration and figure 2-9 shows a switch-based network configuration.

There are several interconnects used in distributed memory systems, with some of the main ones being Ethernet [25], InfiniBand [2], and Intel Omni-Path [20]. These interconnects vary in design, latency, bandwidth, price, manufacturer, etc.

## 2.2.2 High Performance Distributed Memory Code

The main difference between programming shared memory systems and distributed memory systems is the explicit communication required in distributed systems. Communication is used for both synchronization and data transfer, so it is highly likely that a distributed program will have some form of communication. We focus on the data transfer component in this work.

### Models for Managing Distributed Memory

Several models exist for programming on distributed memory systems. A big difference between many of the models is how they present the memory address space to the programmer. Some models presented a unified view of the memory, making

Figure 2-8: Bus-based distributed system.

Figure 2-9: Switch-based distributed system.

it look like one big shared memory system. Often, these systems will transparently handle data transfers by adding in the appropriate functions where data is needed. Other models, such as PGAS, provide a unified view, but with special constraints on the memory access. This gives more control to the programmer in managing the memory. At the lowest level, there are models like message passing, which present the address space as is and programmers are in charge of managing all the data transfers.

PGAS Model PGAS, which stands for partitioned global address space, is a model that looks at distributed memory as a global address space and breaks it into private and shared addresses [7]. It gives a similar representation as a shared memory system. Programmers can assign threads to different operations, where the threads are associated with the different memories in the distributed system. The underlying software handles all communication implicitly. Example languages for this model include UPC [15], Titanium [59], and Co-Array Fortran [32].

Message Passing Model In this model, the programmer is responsible for distributing work among nodes and handling all of the data transfers. Nodes communicate by sending *messages* to each other. Example implementations for this model include OpenMPI [14] and MVAPICH [39]. The work in this thesis utilizes the message passing model.

The most common version of the message passing model is *MPI*, which stands for message passing interface. It is a specification for parallel programming, with a focus on distributed memories. Implementations of the specification provide a software solution for dealing with explicit communication in distributed systems.

MPI can also be used for shared memory parallelization, but other tools, such as OpenMP, remain favored for that area.

At a high-level, MPI launches multiple copies of a program, giving many different processes that (likely) need to communicate with each other. The programmer specifies how the processes cooperate and coordinate with each other. In the program, the user can use a process id to condition certain parts of the code based on the current

```

int main() {

2

MPI_Init();

3

int rank;

4

MPI_get_rank(&rank);

if (rank == 0) {

5

6

printf("My rank is 0\n");

char *msg = "Hello from rank 0";

7

8

MPI_Send(msg, 18, MPI_CHAR, 1 /*dst rank*/, ...);

9

printf("Rank 0 sent message to rank 1\n");

} else { // rank == 1

10

11

printf("My rank is 1\n");

12

char msg[18];

13

MPI_Recv(msg, 18, MPI_CHAR, 0 /*src rank*/, ...);

printf("Rank 1 received message %s from rank 0\n", msg);

14

}

15

16

MPI_Finalize();

17 }

```

Figure 2-10: Simple MPI program with two ranks.

id. This way, the user has complete control over which process executes which part of the code. If the user does not supply any explicit synchronization, the individual processes would run completely concurrently.

Figure 2-10 shows a simple example of writing a program that runs in parallel with two processes. One process sends data (known as a message) to the other process which receives the message. An MPI rank is a unique identifier of an MPI process. By default, each MPI process will be assigned a unique, contiguous integer starting from 0. The rank is one of the most useful components in MPI. First, it can be used to condition parts of the code. In the figure, the if block shows an example of this. Depending on the rank of the process, we want to do one of two things: either we want to send data to the other rank (rank 0 sends to rank 1 using MPI\_Send), or we want to receive that data (rank 1 receives from rank 0 using MPI\_Recv). The rank is also used to specify which other processes to communicate with. This can be seen in the MPI\_Send and MPI\_Recv on lines 8 and 13.

Going into more detail, we are concerned with MPI functions for two-sided communication. In two-sided communication, two ranks communicating with each other must explicitly coordinate: one process needs to initiate a send, and the other needs to initiate a receive. Based the category of the MPI function, communication may also require explicit synchronization. There are four main categories of communication functions in MPI: blocking, non-blocking, synchronous, and asynchronous. Blocking and non-blocking deal with how a thread's execution proceeds after making an MPI function call. Synchronous and asynchronous define what it means for an MPI function to complete. Synchronous and asynchronous only apply to sends, whereas blocking and non-blocking apply to both sends and receives.

- 1. **Blocking**: Control does not return to the calling thread until the MPI function has completed.

- 2. **Non-blocking**: Control immediately returns to the calling thread; it does not wait until it is complete. Explicit synchronization is needed to check when the MPI function has actually completed.

- 3. **Synchronous**: The MPI send is complete when it has transferred all the data froms its send buffer, and the receive has put all of the transferred data into its own buffer.

- 4. **Asynchronous**: The MPI send is complete when it has transferred all the data from its send buffer.

Sends in MPI can be the following combinations: blocking and synchronous (MPI\_Ssend), blocking and asynchronous (MPI\_Send), nonblocking and synchronous (MPI\_Issend), and nonblocking and asynchronous (MPI\_Isend). Receives can be blocking (MPI\_Recv) or non-blocking (MPI\_Irecv). MPI provides additional functions to query the status of nonblocking operations, such as MPI\_Wait. MPI\_Wait will block the calling thread until the specified operation has completed.

All messages sent between a given pair of ranks using these functions arrive in FIFO order. However, there is no guarantee on the ordering of messages across ranks. For example, consider the following scenario with two ranks, r1 and r2, and four messages, m1, m2, m3, and m4.

1. r1 sends m1 to r2.

- 2. r1 sends m2 to r3.

- 3. r1 sends m3 to r2.

- 4. r1 sends m4 to r3.

In this case, r2 is guaranteed to receive message m1 before m3 and r3 is guaranteed to receive m2 before m4. However, r2 could receive both m1 and m3 before r3 receives anything. Or r3 could receive both m2 and m4 before r2 receives any messages. Any interleaving (that still preserves FIFO ordering between a pair of ranks) could happen. MPI provides an optional function argument called a message tag that can be used to differentiate between messages.

### **Optimizing MPI Communication**

Done naively, communication can easily become the bottleneck in a distributed program. A big part of getting good performance is overlapping communication with computation. With blocking communication, the calling thread cannot proceed until the communication is finished, so it cannot do any other useful work in the meantime. However, with non-blocking communication, the thread can do other useful work (assuming there is some) instead of waiting for the communication to finish.

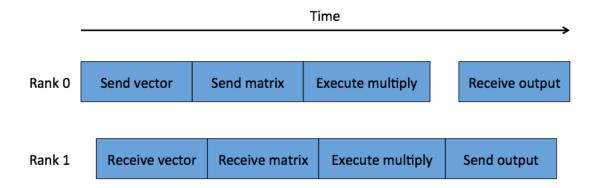

Consider the example code in figures 2-11 and 2-13. Both figures give code for performing a distributed matrix-vector multiply. We assume that there are two ranks, r0 and r1, and the data for the matrix and vector initially reside on the machine running the process for r0. We will have each rank operate on half of the matrix. This means that r0 must send the vector and half of the matrix to r1, and then r1 must send its results back to r0. We assume that data is row-major, and our matrix dimension is M rows by N columns. The difference between the two sets of code is that 2-11 uses blocking communication and 2-13 uses a combination of blocking and non-blocking communication. The blocking version starts by sending the entire vector from r0 to r1 on line 6. In line 7, r0 the entire first half of the matrix to r1. r0 must will block until the sends complete, so it cannot execute its multiply in the loop nest at line 8 until those sends are done. r0 has no overlap of communication and

```

1

MPI_Init(); int rank; MPI_get_rank(&rank);

3

if (rank == 0) {

4

vector = <read from file>; matrix = <read from file>

output = (float*)malloc(sizeof(float)*M);

5

6

MPI_Send(vector, N, MPI_FLOAT, 1, ...);

7

MPI_Send(matrix, (M/2)*N, MPI_FLOAT, 1, ...);

8

for (int r = M/2; r < M; r++) {

9

float sum = 0.0f;

10

for (int c = 0; c < N; c++) {

11

sum += matrix[r*N + c] * vector[c];

12

13

output[r] = sum;

14

MPI_Recv(output, M/2, MPI_FLOAT, 0, ...);

15

} else { // rank == 1

16

17

vector = (float*)malloc(sizeof(float)*N);

18

matrix = (float*)malloc(sizeof(float)*(M/2)*N);

19

output = (float*)malloc(sizeof(float)*M/2);

MPI_Recv(vector, N, MPI_Float, 0, ...);

20

21

MPI_Recv(matrix, (M/2)*N, MPI_FLOAT, 0, ...);

22

for (int r = 0; r < M/2; r++) {

23

float sum = 0.0f;

for (int c = 0; c < N; c++) {</pre>

24

sum += matrix[r*N + c] * vector[c];

25

26

27

output[r] = sum;

28

29

MPI_Send(output, M/2, MPI_FLOAT, 0, ...);

30

31

MPI_Finalize();

```

Figure 2-11: Two process distributed matrix-vector multiply using blocking communication.

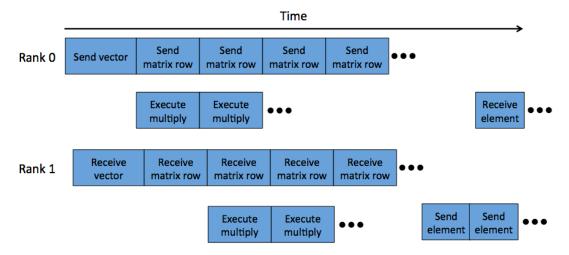

Figure 2-12: Timeline showing sequential communication within a rank due to the use of blocking functions.

computation here. r0's last job is to get the results from r1 and put them in the final output array. This occurs at line 15.

r1 operates similarly to r0, except it receives the messages from r0 (lines 20 and 21) and then sends its results to r0 (line 29). Like r0, r1 cannot begin computing the multiply starting at line 22 until its receive is complete. So r1 also does not have any overlap of communication and computation.

Figure 2-12 shows an approximate (not-to-scale) timeline of execution for r0 and r1. Each rank runs concurrently, but the actual operations within a rank run sequentially, so there is no overlap.

The combined blocking and non-blocking version takes advantage of the ability to overlap communication and computation. r0 starts the same and transfers the vector all in one message on line 6. For the matrix, it sends one row of data at a time (line 10), so a total of M/2 messages are sent. Since the send is non-blocking, it immediately returns and r0 executes the multiply with its current row. r0 ends with getting the output from r1 as before, but it first needs to make sure all its non-blocking sends finished before launching more operations (this is the MPI\_Waitall function on line 15). MPI\_Request objects contain information on the status of functions, so MPI wait functions query these to see if an operation is complete. r0 finishes by receiving the output from r1 with a non-blocking function followed by another MPI\_Waitall on lines 18 and 20.